# Learning EPPGAS

DIGITAL DESIGN FOR BEGINNERS WITH MOJO AND LUCID HDL

# O'REILLY®

# Learning FPGAs

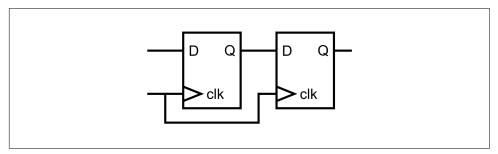

Learn how to design digital circuits with FPGAs (field-programmable gate arrays), the devices that reconfigure themselves to become the very hardware circuits you set out to program. With this practical guide, author Justin Rajewski shows you hands-on how to create FPGA projects, whether you're a programmer, engineer, product designer, or maker. You'll quickly go from the basics to designing your own processor.

Designing digital circuits used to be a long and costly endeavor that only big companies could pursue. FPGAs make the process much easier, and now they're affordable enough even for hobbyists. If you're familiar with electricity and basic electrical components, this book starts simply and progresses through increasingly complex projects.

- Set up your environment by installing Xilinx ISE and the author's Mojo IDE

- Learn how hardware designs are broken into modules, comparable to functions in a software program

- Create digital hardware designs and learn the basics on how they'll be implemented by the FPGA

- Build your projects with Lucid, a beginner-friendly hardware description language, based on Verilog, with syntax similar to C/C++ and Java

**Justin Rajewski** is the owner of Embedded Micro, a company focused on creating user-friendly development boards. A graduate of Stanford University, he's the creator of the Mojo, an FPGA development board targeted specifically at beginners.

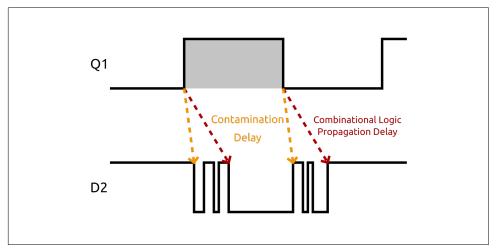

"Justin became famous among Stanford engineering students for building a system for simplifying the complex process of digital design with FPGAs. Everything from the language to the IDE to the meticulous routing of the circuit board was designed by one thoughtful architect. The book you are now holding is the culmination of years of his independent and creative thought, and could very well change the way we think about and work with embedded systems."

**—Dave Deriso**MSE in Applied Math from Stanford

US \$49.99 CAN \$65.99 ISBN: 978-1-491-96549-8

Twitter: @oreillymedia facebook.com/oreilly

# **Learning FPGAs**

Digital Design for Beginners with Mojo and Lucid HDL

Justin Rajewski

#### Learning FPGAs

by Justin Rajewski

Copyright © 2017 Justin Rajewski. All rights reserved.

Printed in the United States of America.

Published by O'Reilly Media, Inc., 1005 Gravenstein Highway North, Sebastopol, CA 95472.

O'Reilly books may be purchased for educational, business, or sales promotional use. Online editions are also available for most titles (<a href="http://oreilly.com/safari">http://oreilly.com/safari</a>). For more information, contact our corporate/institutional sales department: 800-998-9938 or <a href="mailto:corporate@oreilly.com">corporate@oreilly.com</a>.

Editors: Brian Jepson and Jeff Bleiel Production Editor: Nicholas Adams Copyeditor: Sharon Wilkey Proofreader: Amanda Kersey Indexer: Wendy Catalano

Interior Designer: David Futato

Cover Designer: Karen Montgomery

Illustrator: Rebecca Demarest

August 2017: First Edition

**Revision History for the First Edition** 2017-08-02: First Release

See http://oreilly.com/catalog/errata.csp?isbn=9781491965498 for release details.

The O'Reilly logo is a registered trademark of O'Reilly Media, Inc. *Learning FPGAs*, the cover image, and related trade dress are trademarks of O'Reilly Media, Inc.

While the publisher and the author have used good faith efforts to ensure that the information and instructions contained in this work are accurate, the publisher and the author disclaim all responsibility for errors or omissions, including without limitation responsibility for damages resulting from the use of or reliance on this work. Use of the information and instructions contained in this work is at your own risk. If any code samples or other technology this work contains or describes is subject to open source licenses or the intellectual property rights of others, it is your responsibility to ensure that your use thereof complies with such licenses and/or rights.

978-1-491-96549-8

[LSI]

# **Table of Contents**

| Pre | eface                                                                                                                                                                                                                                                 | vii                                                      |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 1.  | Introduction.  The Mojo FPGAs Versus Microcontrollers: A Comparison Setting Up Your Environment Installing ISE Installing the Mojo IDE                                                                                                                | . 1<br>3<br>7<br>8<br>14                                 |

|     | Mojo IDE Settings                                                                                                                                                                                                                                     | 15                                                       |

| 2.  | Your First FPGA Project Creating a New Project Understanding Modules Representing Values Using Always Blocks Connecting the Button Building Your Project Loading Your Project Some Notes on Hardware Duplication Array Indexing Always Block Priority | 19<br>21<br>22<br>23<br>25<br>26<br>27<br>30<br>30<br>31 |

| 3.  | Combinational Logic                                                                                                                                                                                                                                   | 33<br>33<br>36<br>39<br>40                               |

|    | Math                                                 | 41  |

|----|------------------------------------------------------|-----|

|    | Common Subcircuits                                   | 44  |

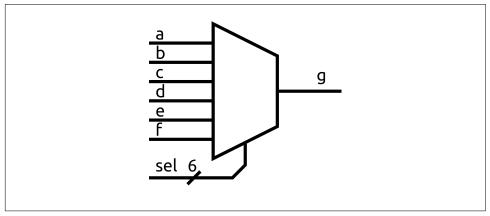

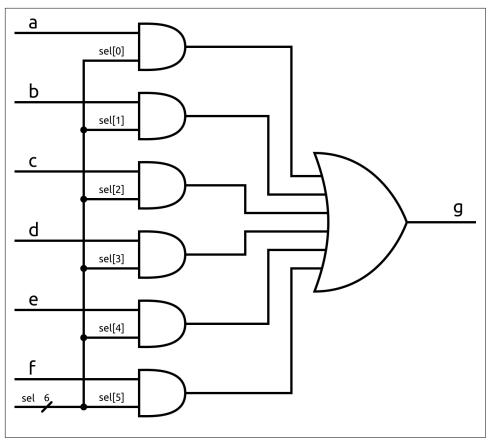

|    | Multiplexers                                         | 44  |

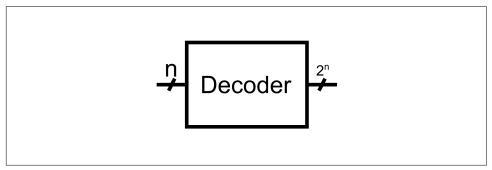

|    | Decoders                                             | 46  |

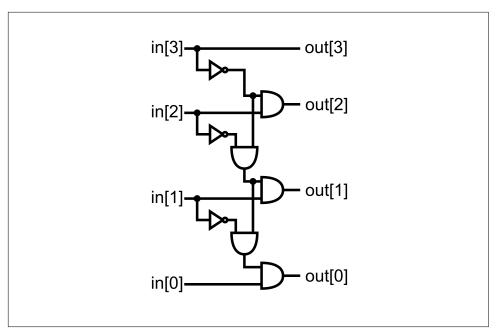

|    | Encoders                                             | 47  |

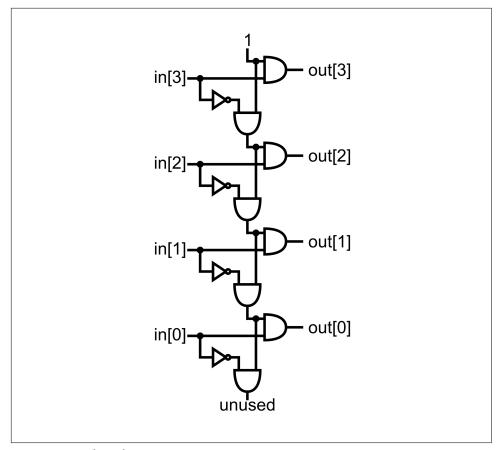

|    | Arbiters                                             | 47  |

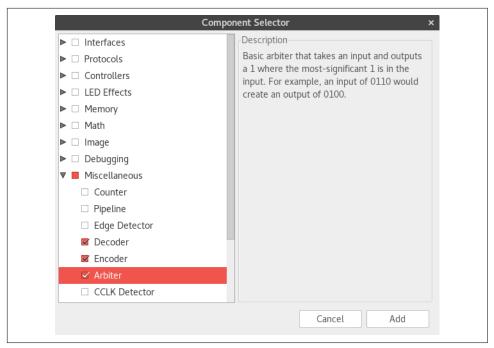

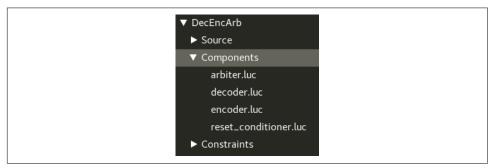

|    | Decoder, Encoder, and Arbiter Example                | 50  |

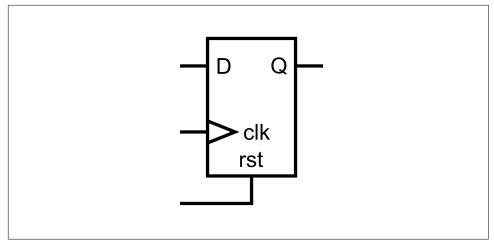

| 4. | Sequential Logic                                     | 55  |

|    | Feedback Loops and Flip-Flops                        | 56  |

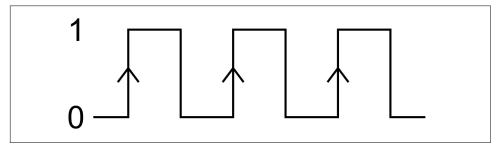

|    | Clocks                                               | 57  |

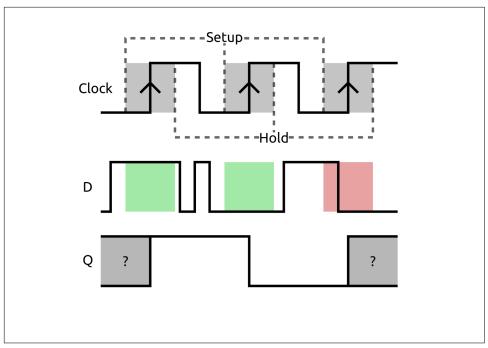

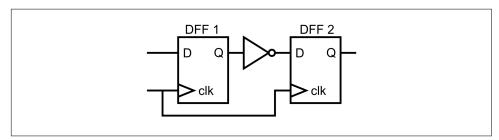

|    | Timing and Metastability                             | 61  |

|    | External Inputs                                      | 66  |

|    | Add the Components                                   | 67  |

|    | Instantiating a Module                               | 69  |

|    | Checking Timing                                      | 71  |

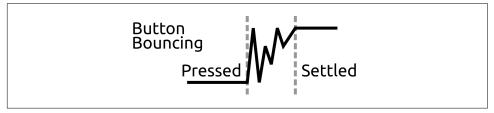

|    | Bouncy Buttons and Edges                             | 72  |

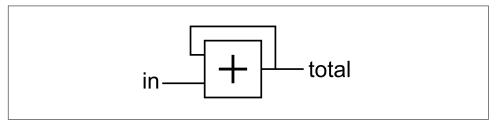

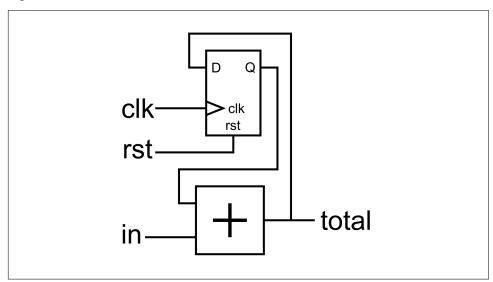

|    | Running Total                                        | 73  |

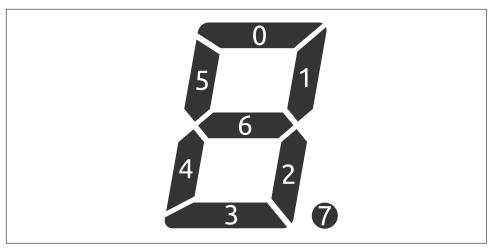

| 5. | Seven-Segment LED Displays and Finite-State Machines | 75  |

|    | Single Digit                                         | 76  |

|    | Lookup Tables                                        | 79  |

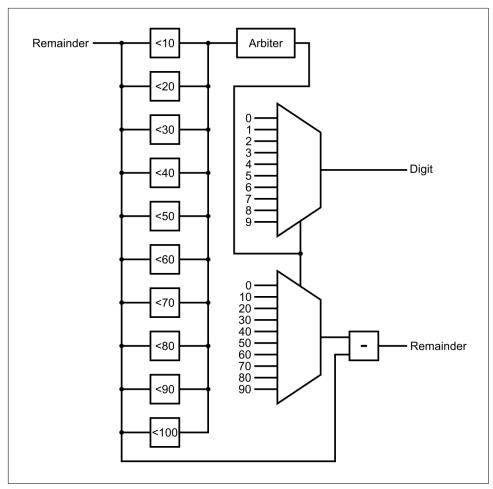

|    | Binary to Decimal                                    | 83  |

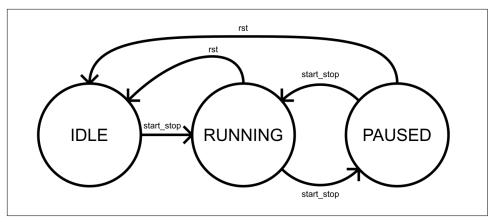

|    | The Finite-State Machine                             | 87  |

|    | The Stopwatch                                        | 87  |

| 6. | Hello AVR                                            | 91  |

|    | The AVR Interface                                    | 91  |

|    | Sending and Receiving Data                           | 92  |

|    | ROMs                                                 | 92  |

|    | The Greeter                                          | 93  |

|    | Getting Personal with RAM                            | 95  |

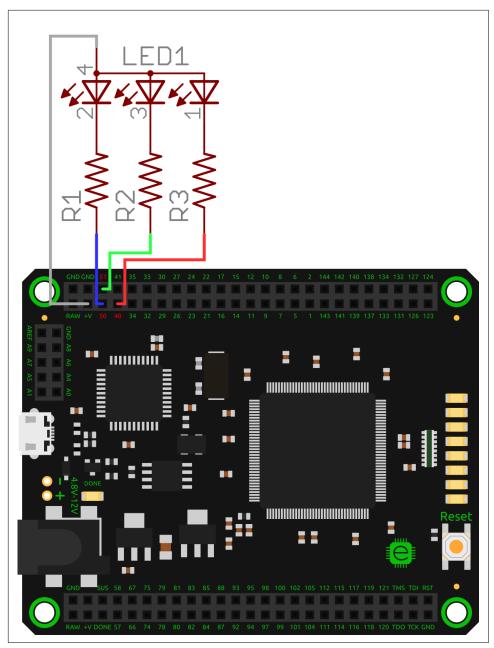

| 7. | Mixing Colors with an RGB LED.                       | 101 |

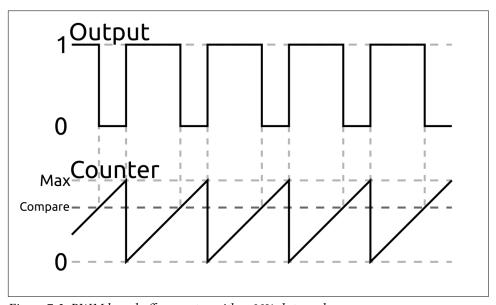

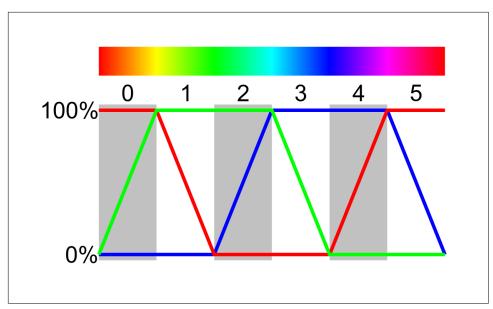

|    | -                                                    | 103 |

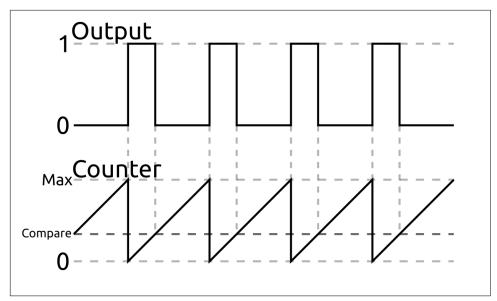

|    | Getting Fancy with PWM                               | 105 |

|    |                                                      | 111 |

| 8. | Analog Inputs                                        | 117 |

|    | , , , , , , , , , , , , , , , , , , ,                | 117 |

|    |                                                      | 119 |

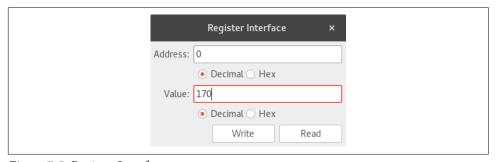

| 9.  | A Basic Processor                              | 121 |

|-----|------------------------------------------------|-----|

|     | What Is a Processor?                           | 122 |

|     | Instruction Sets                               | 122 |

|     | Memory                                         | 122 |

|     | Initial Design                                 | 123 |

|     | NOP                                            | 123 |

|     | LOAD and STORE                                 | 123 |

|     | SET                                            | 124 |

|     | LT and EQ                                      | 124 |

|     | BEQ and BNEQ                                   | 124 |

|     | The ALU                                        | 124 |

|     | The Program Counter                            | 125 |

|     | The Processor                                  | 125 |

|     | The Program                                    | 128 |

|     | The Assembler                                  | 130 |

| 10. | FPGA Internals                                 | 133 |

|     | General Fabric and Routing Resources           | 133 |

|     | Special Primitives                             | 135 |

|     | Block RAM (Memory)                             | 135 |

|     | Math                                           | 140 |

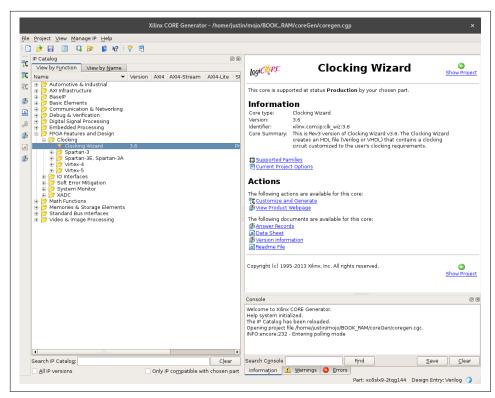

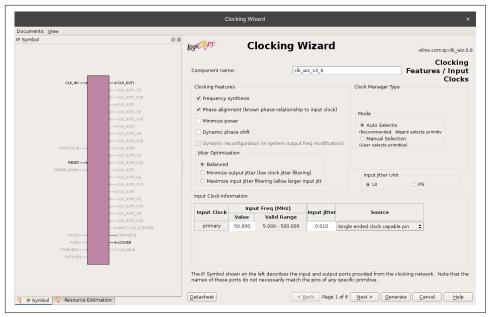

|     | Clocking                                       | 140 |

|     | Special I/O Features                           | 143 |

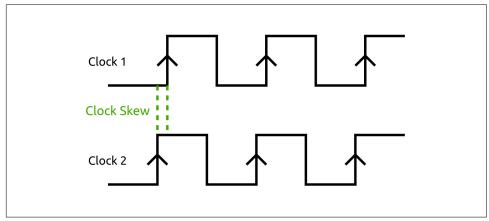

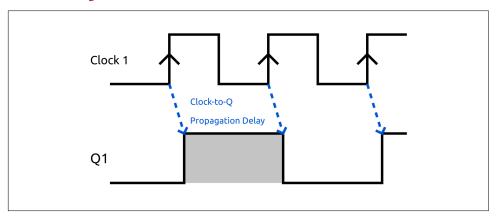

| 11. | Advanced Timing and Clock Domains              | 145 |

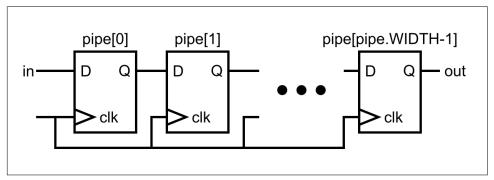

|     | Breaking Timing and Fixing It with Pipelining  | 145 |

|     | Crossing Clock Domains                         | 150 |

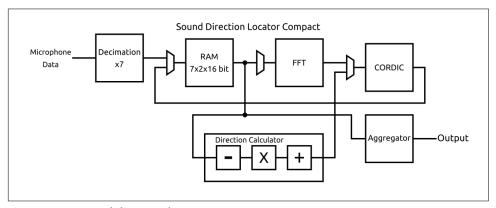

| 12. | Sound Direction Detection: An Advanced Example | 155 |

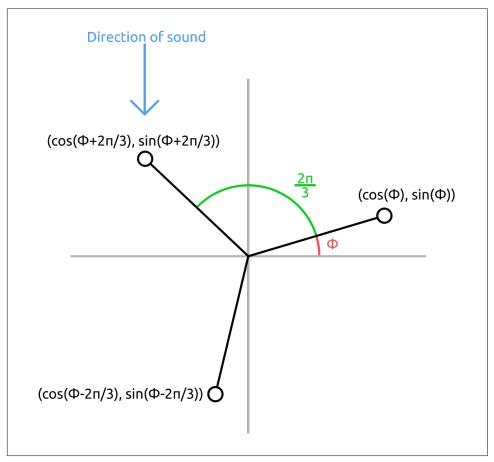

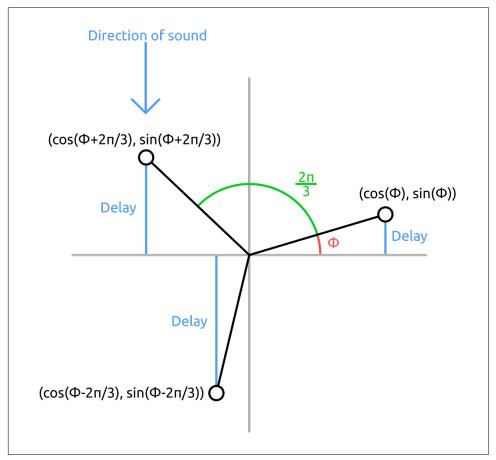

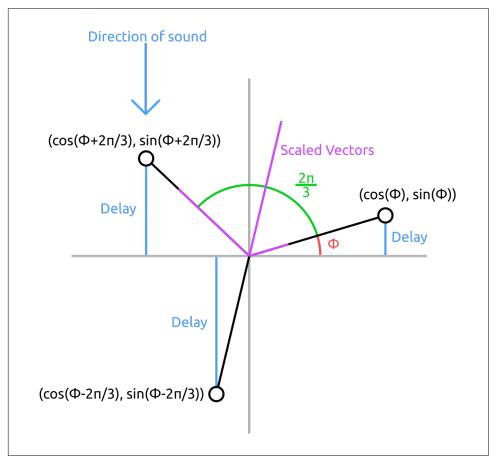

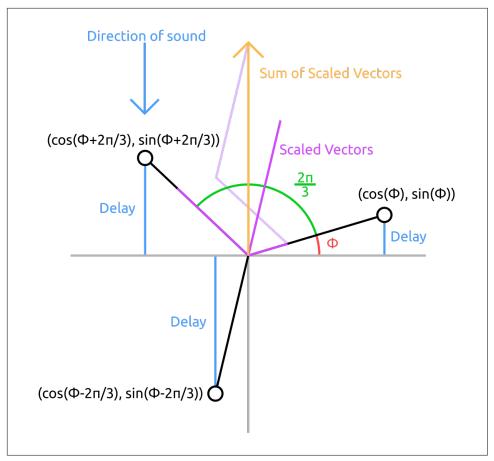

|     | Theory of Operation                            | 156 |

|     | Implementation Overview                        | 162 |

|     | Implementation                                 | 164 |

|     | PDM Microphones                                | 164 |

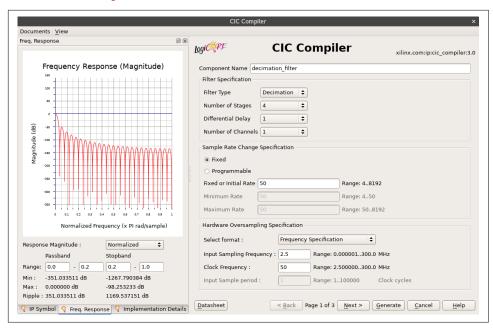

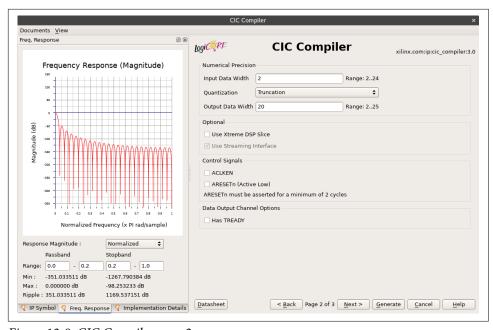

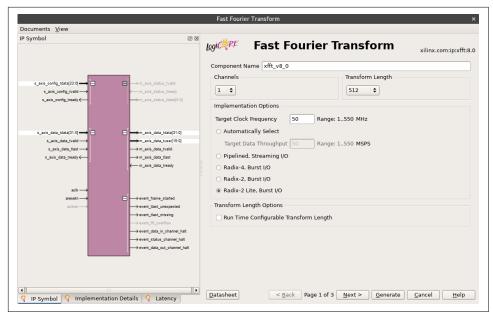

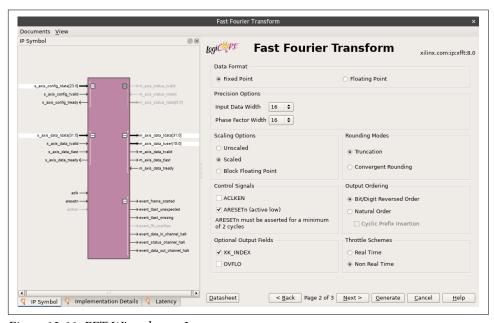

|     | FFT                                            | 168 |

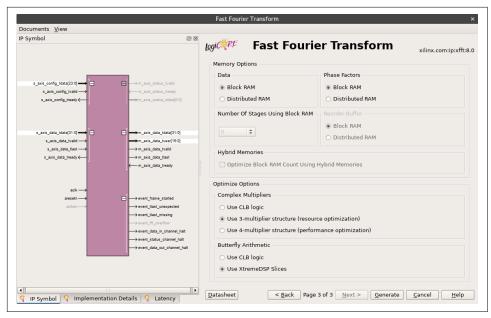

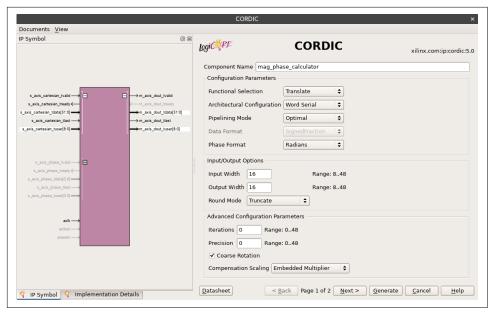

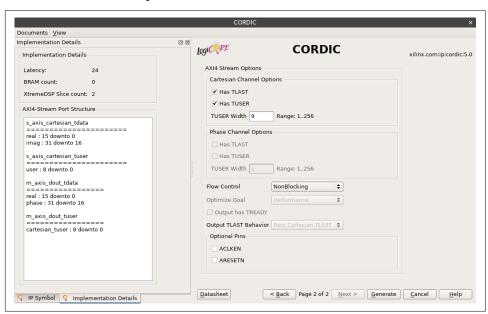

|     | CORDIC                                         | 171 |

|     | CAPTURE State                                  | 174 |

|     | FFT State                                      | 175 |

|     | DIFFERENCE State                               | 177 |

|     | AGGREGATE State                                | 180 |

| 13. | Lucid Reference                                | 183 |

|     | Lucid Quick Reference                          | 184 |

|    | Parameter Lists              | 185 |

|----|------------------------------|-----|

|    | Port Lists                   | 186 |

|    | Module Body                  | 187 |

|    | Expressions                  | 195 |

|    | Signals and Constants        | 195 |

|    | Functions                    | 196 |

|    | Groups                       | 197 |

|    | Array Concatenation          | 197 |

|    | Array Duplication            | 197 |

|    | Array Builder                | 197 |

|    | Bitwise Invert               | 197 |

|    | Logical Invert               | 198 |

|    | Negate                       | 198 |

|    | Multiply                     | 198 |

|    | Divide                       | 198 |

|    | Add and Subtract             | 198 |

|    | Bit Shifting                 | 199 |

|    | Bitwise Operators            | 199 |

|    | Reduction Operators          | 199 |

|    | Comparison Operators         | 200 |

|    | Logical AND and OR           | 200 |

|    | Ternary Operator             | 200 |

|    | Literal Values               | 201 |

|    | Numbers                      | 201 |

|    | Strings                      | 201 |

|    | global Blocks                | 201 |

|    | Array Size and Bit Selection | 202 |

|    | Array Size                   | 202 |

|    | Bit Selectors                | 203 |

|    | Comments                     | 204 |

| A. | Full Modules and Proof       | 205 |

| I  | L                            | 212 |

# **Preface**

Designing digital circuits used to be something that only big companies could afford to do. It used to require creating application-specific integrated circuits (ASICs)—taking weeks or months to produce an actual chip, and requiring piles of cash or wiring together tons of individual chips to perform various logic functions. Then the field-programmable gate array (FPGA) was introduced. FPGAs are programmable logic devices. Unlike an ASIC, the function an FPGA performs is determined at runtime, so an FPGA can be configured to act like just about any digital circuit. However, it wasn't until recently that the cost of FPGAs has dropped to a point where they are now affordable for even hobbyists.

An FPGA allows you to design digital circuits. *Digital circuits* are basically just a bunch of logic gates (and, or, nor, etc.) connected together to perform a specific task. The designs that you create can range from something as simple as a counter that blinks an LED to something as complex as a multicore processor.

This book starts at the very beginning, with setting up your environment and getting an LED to turn on. As you develop your skills, you will learn how to perform more-complicated tasks and eventually design your own basic processor.

The board used in this book is the Mojo (along with the IO Shield). I created the Mojo in 2013 as a simple no-shenanigans FPGA development board for the hobbyist. I ran a Kickstarter to gauge interest and fund the initial round of boards. A lot more excitement than I originally expected resulted and has allowed me to continue working on it. My goal is to build a platform so that anyone who wants to learn about FPGAs—and more generally, digital design—can without having to go to college or having a personal mentor. This book is just another step toward this goal.

# **Expected Background**

This book is going to teach you the basics of digital hardware design. This is not a topic for the complete beginner, and some background information is going to be assumed. You should be familiar with electricity (voltage and current) and basic electrical components (resistors, capacitors, transistors, and LEDs). While not strictly required, some programming background will be helpful, especially if it is with embedded microcontrollers such as an Arduino.

The majority of this book uses Lucid. Lucid is a hardware description language (HDL) that was designed to be beginner friendly and simpler to use with FPGAs than the more traditional Verilog and VHDL languages. Lucid is similar to Verilog in many ways, and our tools actually translate it to Verilog as an intermediate step during the build process. However, it removes some of the quirks that plague Verilog and makes many of the easy-to-make mistakes impossible.

Check out the Lucid Quick Reference guide in Chapter 13.

Lucid shares similar syntax with programming languages such as C/C++ and Java. Being familiar with one of these can help. However, it is important to remember that Lucid is a hardware description language and not a programming language.

It is important to have a solid understanding of binary, hexadecimal, and decimal number systems.

## Conventions Used in This Book

The following typographical conventions are used in this book:

Italic

Indicates new terms, URLs, email addresses, filenames, and file extensions.

#### Constant width

Used for program listings, as well as within paragraphs to refer to program elements such as variable or function names, databases, data types, environment variables, statements, and keywords.

#### Constant width bold

Shows commands or other text that should be typed literally by the user.

#### Constant width italic

Shows text that should be replaced with user-supplied values or by values determined by context.

This element signifies a tip or suggestion.

This element signifies a general note.

This element indicates a warning or caution.

# **Using Code Examples**

A repo of the book example projects is here:

https://github.com/embmicro/book-examples

A repo of all the built-in example projects in the Mojo IDE is here:

https://github.com/embmicro/components-library/tree/master/base/mojo-v3/Lucid

If you are familiar with Git, you can use it to clone the repos. If you aren't, you can follow those links and click the green "Clone or download" button to open a dropdown menu with a link to download a ZIP of all the files.

## How to Contact Us

Please address comments and questions concerning this book to the publisher:

O'Reilly Media, Inc. 1005 Gravenstein Highway North Sebastopol, CA 95472 800-998-9938 (in the United States or Canada) 707-829-0515 (international or local) 707-829-0104 (fax)

We have a web page for this book, where we list errata, examples, and any additional information. You can access this page at <a href="http://bit.ly/learning\_FPGAs">http://bit.ly/learning\_FPGAs</a>.

To comment or ask technical questions about this book, send email to bookquestions@oreilly.com.

For more information about our books, courses, conferences, and news, see our website at http://www.oreilly.com.

Find us on Facebook: <a href="http://facebook.com/oreilly">http://facebook.com/oreilly</a>

Follow us on Twitter: <a href="http://twitter.com/oreillymedia">http://twitter.com/oreillymedia</a>

Watch us on YouTube: http://www.youtube.com/oreillymedia

# Introduction

FPGA stands for *field programmable gate array*. That mouthful is simply trying to tell you that you can program an FPGA over and over (field programmable) and that it is more or less just a large array of logic gates (gate array).

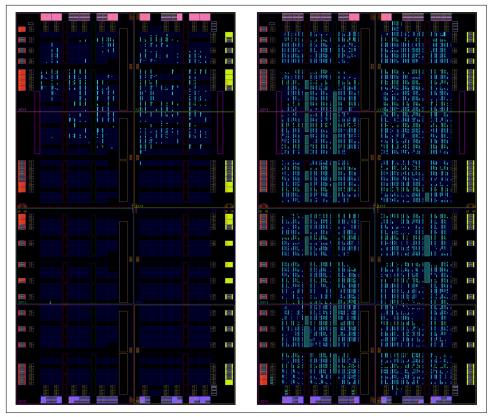

Unless you already know what all that means, it is still not very helpful, so let's break it down a little more. An FPGA belongs to a family of devices known as *programmable logic devices*. These devices allow you to design a digital circuit, and the device will *become* that circuit. This works by configuring small blocks (known as *slices*) to perform logic functions and connecting them together to implement your larger design. A more detailed description of how this all works is covered later. You can reconfigure the FPGA as many times as you want, and each time it will become the new circuit without needing to physically change anything!

In this chapter, we will explain a little more about what FPGAs are and what they are good at. We will also walk you through all the steps to set up the necessary software on Windows or Linux. Unfortunately, Macs are not supported by Xilinx's tools, but you can work through a virtual machine running a compatible operating system. You can do with this with VirtualBox and Ubuntu, both of which are free. With a working environment, we will work through a basic project that will turn on an LED when a button is pressed.

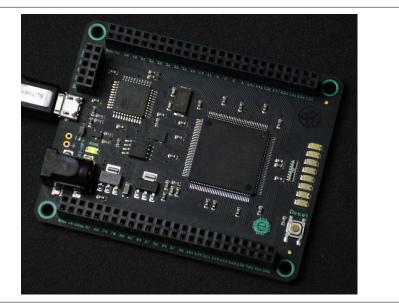

# The Mojo

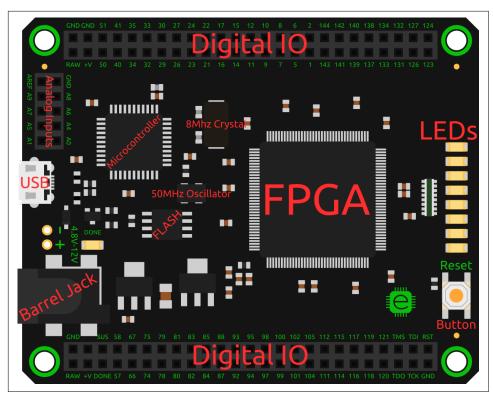

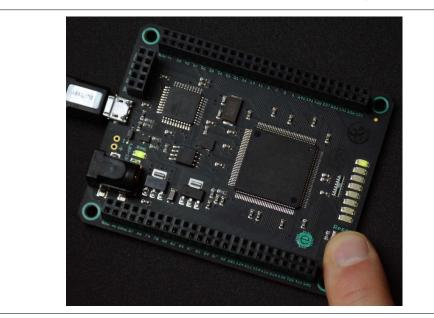

Throughout this book, we will be using the Mojo and its IO Shield. The *Mojo*, shown in Figure 1-1, is an FPGA development board that is relatively inexpensive and requires only a computer and a micro USB cable to use. Unlike many other FPGA development boards, it is fairly minimal, with most of the FPGA's pins broken out onto easy-to-use 0.1" headers (a total of 84 digital I/O pins).

1

Figure 1-1. The Mojo

The Mojo also has an Arduino-compatible microcontroller whose main function is to program the FPGA over USB. However, once the FPGA is programmed, the microcontroller can be used as an ADC (eight analog inputs are broken out) and a USB-to-serial interface for your FPGA designs. Beyond the other bare necessities such as a 50 MHz oscillator, the Mojo features eight LEDs and a button (commonly used as a reset).

The I/O on the Mojo is all at 3.3 V and is not 5 V tolerant. Power can be supplied via the USB port, the barrel jack, the two holes, or the RAW input on the large headers. The supplied power should be between 4.8 V–12 V, with 5 V being the recommended voltage. You can connect an external power supply and the USB port at the same time, as the USB port is protected by a diode.

You can find more information and order the Mojo from Embedded Micro.

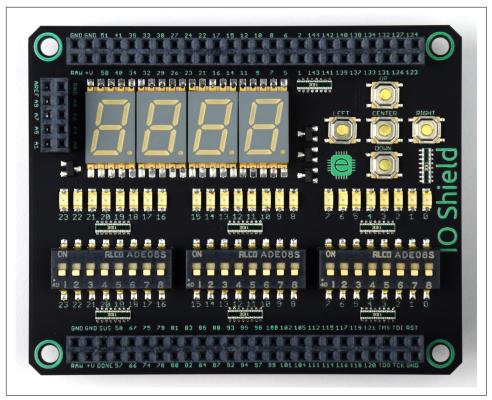

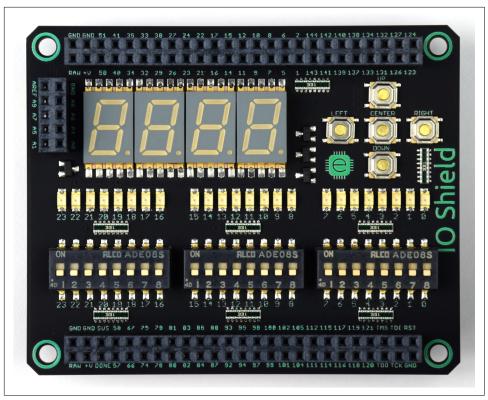

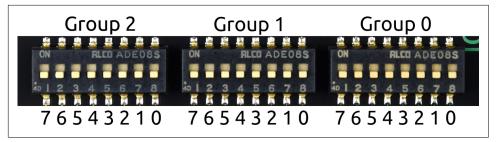

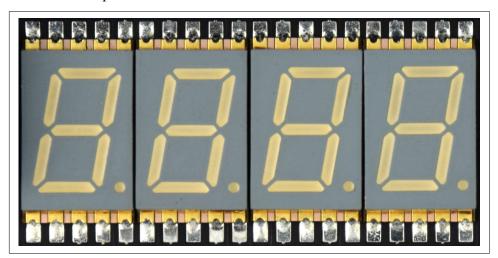

The *IO Shield*, shown in Figure 1-2 is an add-on board that stacks on top of the Mojo. It features 4 7-segment LED digits (like the display on your microwave), 24 LEDs, 24 switches, and 5 buttons. It is a great board for working through example projects. You can find more information and order your own from Embedded Micro.

Figure 1-2. IO Shield

# **FPGAs Versus Microcontrollers: A Comparison**

FPGAs and microcontrollers are often compared. This is especially true for people coming from a background of working with boards such as the Arduino or Raspberry Pi. An analogy that I particularly like is to think of a microcontroller as a person. People are flexible. You can teach someone to do almost any task, and his arms and hands are capable of manipulating basically anything. However, people can really focus on only one thing at a time, and unfortunately, we have only two hands. An FPGA, on the other hand, is like an assembly line. You can tailor it specifically for the exact job it needs to do. You can have many stages in the line that are all working at the same time, independent of one another.

FPGAs have been becoming more popular recently and have started appearing in more mainstream news. It used to be that if you wanted to improve the performance of an application, you simply bought or waited for a faster processor. However, in recent years, even though Moore's law continues, processor performance has largely stalled with the extra transistors being used to cram more cores into a single chip.

Because of this, people have started turning to FPGAs to accelerate tasks by creating custom hardware.

When you are working with FPGAs, you are designing hardware, not software. To make this a little clearer, let's look at something that could be done with either an FPGA or a microcontroller: turning on an LED when you press a button. If you were to do this with a microcontroller, such as an Arduino or Raspberry Pi, the code to do this would read the button input, and if it is pressed, turn the LED on, and otherwise turn it off. This would keep happening over and over in a loop. Read button, update LED, read button, update LED, and so on. The problem with this is that the processor is now spending all of its time keeping the LED up to date with the current value of the button.

If you did the same project with an FPGA, you could simply connect the LED and the button through the FPGA. Since they are connected, there is no loop, and there is no code; the LED just turns on when the button is pressed. Now, if you wanted to change it up an, say, turn on the LED when the button is not being pressed, with a microcontroller you just change the test condition. However, with an FPGA, you can simply insert a NOT gate between the LED and button.

With the microcontroller, the processor is fully busy with this trivial task. What happens when you want it to also do something else, such as read other inputs or perform calculations? The processor has to juggle the tasks, spending only finite amounts of time on each one. As the complexity of your other code grows, the amount of time the processor has to spend checking the button and updating the LED shrinks, making it take longer and longer for the LED to turn off after you press the button.

FPGAs are not like this. Instead, with an FPGA, since it is all hardware, the circuit you designed to read the button and update the LED will operate completely independently of anything else you throw in your design. You could have another part of the FPGA crunching some serious numbers, but the LED will still be just as responsive as before.

Although you can usually do the same task with a microcontroller or an FPGA, there is usually a clear better choice. Things that require a lot of complex decision-making or sequential operations are commonly better candidates for microcontrollers. Things that can be done in stages or have a regular set pattern are great for FPGAs. This is just a rule of thumb, but the takeaway is that custom hardware and a processor fill different needs, and it's often great to have both (and the Mojo does).

Another powerful feature of FPGAs is that they can read or write every I/O pin every clock cycle. With a microcontroller, you are typically limited to reading registers of 8 or 32 bits that correspond to I/O pins. If you need to sample more pins, you need to do it over multiple cycles, which may not be ideal. This makes it really easy to drive things that require a lot of I/O, such as LED matrices or a ton of servos. It's also possible to read and write I/O pins at much higher rates. The FPGA on the Mojo is capable of I/O speeds up to 950 MHz; that's 950 million reads or writes a second! Compare this to a typical Arduino's max I/O toggle rate of around 3-4 MHz (with a 16 MHz clock), and this is achievable only if you dedicate all the processing time to toggling the pin.

Table 1-1 summarizes some of the key distinctions.

*Table 1-1. FPGA versus microcontrollers*

| Micro                                                                                   | FPGA                                                                                   |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Write software.                                                                         | Design hardware.                                                                       |

| Typically executes one instruction at a time.                                           | All parts of your circuit can operate independently.                                   |

| Fixed maximum clock speed.                                                              | Maximum clock speed is dependent on your design.                                       |

| A handful of I/O pins that can be accessed in small groups (typically eight) at a time. | Many I/O pins that can all be accessed simultaneously.                                 |

| Usually store programs in nonvolatile (persistent) memory.                              | RAM based and needs to be programed after power on (the Mojo does this automatically). |

| Often very power efficient with advanced sleep modes.                                   | Power usage depends on your design but typically requires more than a microcontroller. |

| Fixed peripherals that limit the devices you can connect.                               | Can interface with virtually any digital device.                                       |

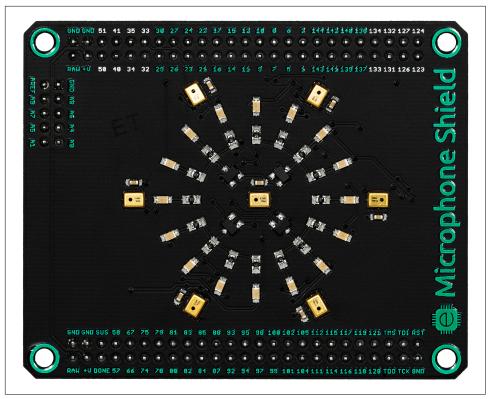

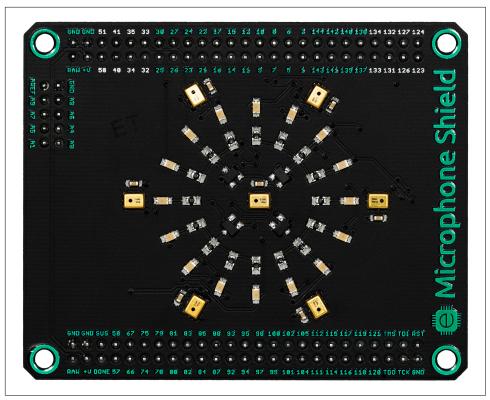

So what can you do with an FPGA that you can't with a microcontroller? In Chapter 12, we use seven microphones to detect the directions of potentially multiple sound sources. Figure 1-3 shows the layout of the microphones on the board. This is done by calculating the delays between all the microphones for various frequencies and piecing them together to get an image of the sounds around the microphone array. A crucial step is sampling all the microphones at exactly at the same time. With an FPGA, it is fairly trivial to exert precise control over I/O pins. Once the samples are gathered, the FPGA is capable of performing all the calculations incredibly fast. The result is a sensor that constantly listens to its surroundings, generating direction data at over 80 Hz (limited by the sample acquisition time and not the processing time).

Figure 1-3. Microphone Shield

One of my favorite projects with the Mojo was a hexapod, shown in Figure 1-4. A hexapod is a 6-legged robot that usually has 3 servos per leg (18 total) plus 1 or 2 more for the "head." Controlling all these servos can be pretty tricky. Many people have made hexapods without using FPGAs. However, even if all you want to do is make the hexapod walk, you still need to get external servo controllers to control that many servos. With an FPGA, you simply add a servo controller as part of your FPGA design, without the need for any external hardware. With an FPGA, every single I/O pin can control a servo. What made the FPGA in this project really necessary was the addition of a 2-megapixel camera (1,600 x 1,200) that took 15 pictures per second (nearly 29 million pixels per second!). The images from the camera were streamed directly into the FPGA, which performed blob detection (to look for red objects). By having the robot detect red objects, it was able to move its body and "watch" a red ball as someone moved it around. You can check it out in action on YouTube.

Figure 1-4. Hexapod

# **Setting Up Your Environment**

The first step on your journey to becoming a digital hardware master is to install all the necessary tools. The FPGA on the Mojo is a Spartan 6 XC6SLX9 from Xilinx. Because of this, you need to download and install Xilinx's tools to synthesize (build) your projects into configuration files (often called bit files) for the FPGA. Xilinx's tools are a bit clunky, so we will be using the Mojo IDE to do all the work. Although you won't need to use Xilinx's tools directly, the Mojo IDE relies on them to build your designs.

## **Synthesize**

We use the term synthesize instead of compile and link, as you would for code, because the tools for hardware are quite different from software. With software, each file is compiled into instructions that are more or less a direct translation of your code. Each file is then linked with the other compiled files to create your program.

With an FPGA, the tools use your design files as a description of the behavior the circuit needs to have. It then looks at your entire design and synthesizes a circuit that will match its behavior. The tools we are using need to rebuild the entire project if you edit even the smallest thing in a single file. This can be a major headache for bigger FPGAs, when synthesis can take hours or days. Partial resynthesis to speed things up is an active area of development. Luckily for us, most projects on the Mojo synthesize within a few minutes.

The tools require you to be using Windows or Linux. If you're using Windows, Windows 7 or newer is recommended. Although Windows 8 and above isn't officially supported by the tools, it should still work with some minor workarounds. Most versions of Linux should work fine, but CentOS is known to have issues with setting up the Mojo and is not recommended. Ubuntu and its derivatives should work out of the box.

If you have a Mac, you can run Linux in a virtual machine or boot Linux from a USB drive. You can do the same for Windows if you have a license. If going this route, I recommend VirtualBox and Ubuntu. Both are free and known to work.

# Installing ISE

*ISE* is the name of the tool Xilinx provides to build projects for the Spartan 6 family of FPGAs. Xilinx has a newer tool called Vivado, but that doesn't support Spartan 6 devices.

Unfortunately, the installation process for ISE is a bit complicated. You are required to make an account with Xilinx to verify what you are using ISE for and where you live (export restrictions are imposed by the US government). ISE is a fairly large program. The download file is just over 6 GB, and the actual installation requires an additional 16 GB or so of space. After it is installed, you will then need to license it. The FPGA on the Mojo is covered by Xilinx's free WebPACK license, but you still have to get the free license.

Head over to the Xilinx Downloads page. You need to download version 14.7 of ISE. This is the latest and final version. It should already be selected. Scroll down past the Multi-File Download: ISE Design section to ISE Design Suite. In this section, select the full installer for your platform (Linux or Windows). You will likely be prompted to fill out a survey on your reasons for downloading it. Then you will be asked to sign in. Create an account to continue with the download.

If you are on Windows, you need a way to extract the TAR file. Some TAR extractors don't like this archive and fail to extract the entire thing. 7-Zip is known to work and is free. You can download it from the 7-Zip website.

With the files extracted, you need to start the installer. On Windows, double-click the *xsetup* executable. On Linux, you need to run *xsetup* with root privileges:

```

sudo ./xsetup

```

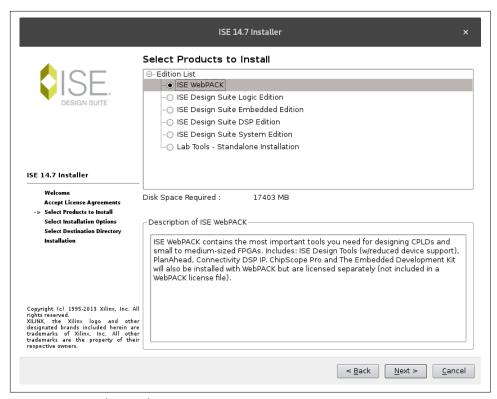

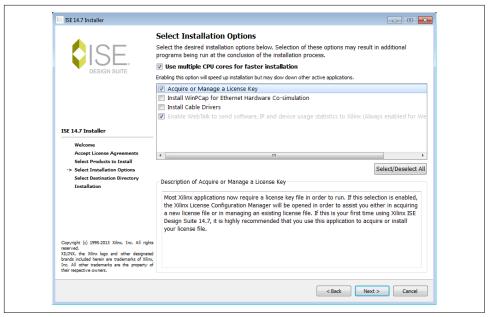

Once in the setup, accept all the license agreements. On the page that asks which edition to install, select ISE WebPACK, as shown in Figure 1-5.

Figure 1-5. ISE edition selection

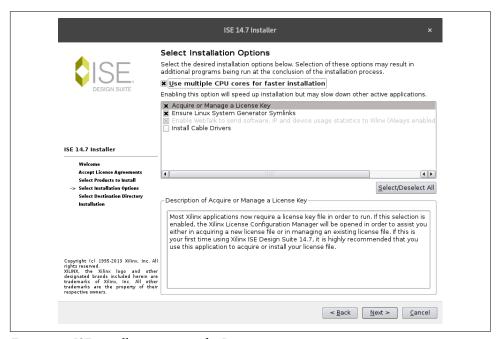

The next page, shown in Figure 1-6, asks which components you want to install. Make sure that Acquire or Manage a License Key is selected. If you are on Linux, make sure Ensure Linux System Generator Symlinks is also selected, as shown in Figure 1-7. You can uncheck the other options. They won't hurt anything if you install them, but they aren't needed. If you run into trouble with the installer, you can try to uncheck "Use multiple CPU cores for faster installation," as it has been reported to cause problems in rare circumstances.

Figure 1-6. ISE installation options for Windows

Figure 1-7. ISE installation options for Linux

On the next page, leaving the installation path as the default will make things a little easier later, but feel free to change it as long as you remember where it is.

If you are using Windows 8.1 or Windows 10 on a 64-bit machine and encounter problems, check out Embedded Micro's ISE Installation Tutorial for other OS specific fixes.

Once the installation is complete, a new window to set up a license *should* open. If for whatever reason it doesn't, you can manually open it by launching ISE and going to  $Help \rightarrow Obtain a License Key.$

On Windows, you can double-click the ISE icon that should now be on your desktop. On Linux, if you installed ISE to the default directory, you can run the following commands to launch it on a 64-bit system:

```

source /opt/Xilinx/14.7/ISE DS/settings64.sh

/opt/Xilinx/14.7/ISE_DS/ISE/bin/lin64/ise

```

To launch ISE on a 32-bit system, use the following:

```

source /opt/Xilinx/14.7/ISE DS/settings32.sh

/opt/Xilinx/14.7/ISE_DS/ISE/bin/lin/ise

```

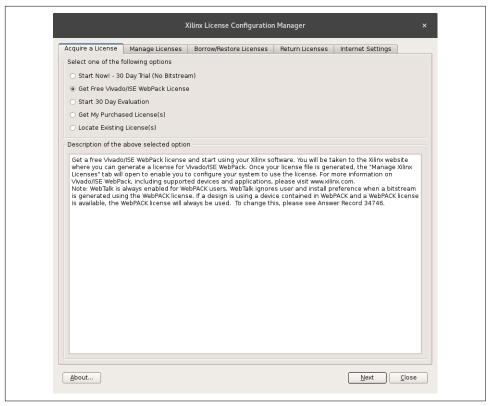

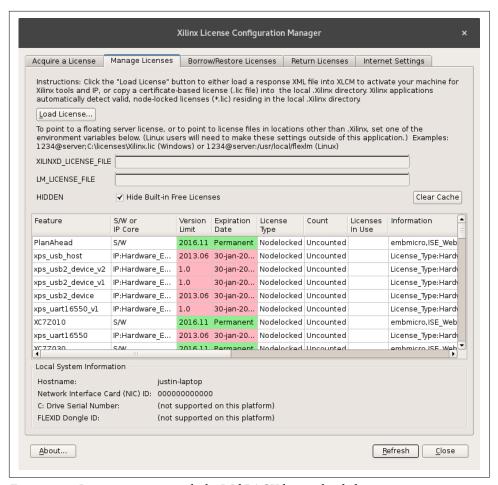

In the Xilinx License Configuration Manager, shown in Figure 1-8, select Get Free Vivado/ISE WebPack License and click Next.

A little dialog box showing your system's information pops up. Click Connect Now to open a web browser to acquire the license. If the button fails to open a browser, you can go to the license page directly.

Figure 1-8. Select the WebPack license

You need to log into your Xilinx account again. When you are on the Product Licensing page, shown in Figure 1-9, select ISE WebPACK License and click Generate Node-Locked License to create your license. If you don't see this option, you may have already generated a license before. In this case, head over to the Manage Licenses tab and download your existing license by using the tiny download button in the bottom-left corner.

| Product                                     |                 | Туре                     | License  | Available<br>Seats | Status  | Subscription<br>End Date |

|---------------------------------------------|-----------------|--------------------------|----------|--------------------|---------|--------------------------|

| Vivado Design Suite: HL WebPACK 2015 and    | Earlier License | Certificate - No Charge  | Node     | 1/1                | Current | None                     |

| Vivado Design Suite (No ISE): 30-Day Evalua | ition License   | Certificate - Evaluation | Node     | 1/1                | Current | 30 days                  |

| ✓ ISE WebPACK License                       |                 | Certificate - No Charge  | Node     | 1/1                | Current | None                     |

| PetaLinux Tools License                     |                 | Certificate - Evaluation | Node     | 1/1                | Current | 365 days                 |

| PetaLinux Tools License, Floating License   |                 | Certificate - Evaluation | Floating | 1/1                | Current | 365 days                 |

| 1                                           |                 |                          | riodding | 272                | Current | 505 days                 |

Figure 1-9. Generate the WebPACK license

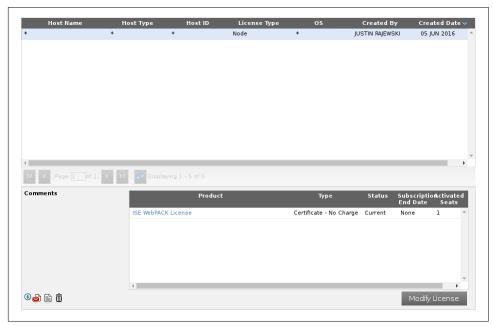

Click through the little pop-up window until the license is created and you are taken to the Manage Licenses tab. On this page, you should see your newly generated license. To download it, click the tiny blue arrow in the lower-left corner, as shown in Figure 1-10.

Figure 1-10. Click the little arrow in the bottom-left corner to download your license

A file named Xilinx.lic should be downloaded.

Back in the Xilinx License Configuration Manager, navigate to the Manage Licenses tab, if you're not already there, and click Load License. Locate the Xilinx.lic file you just downloaded and select it. With the license loaded, the license manager should look like Figure 1-11.

Figure 1-11. License manager with the WebPACK license loaded

Note that it might not look exactly like this, but ISE\_WebPACK and PlanAhead should now be green.

ISE should now be ready to build your projects. You can close any ISE-related windows still open.

# Installing the Mojo IDE

Installing the Mojo IDE is substantially simpler than setting up ISE. Head over to Embedded Micro and download the latest version. If you are on Windows, the installer is the recommended way to go.

The installer is pretty straightforward. Just follow the instructions until everything is installed. At the end of the installation, it should also install the necessary drivers.

On Linux, you just have the files and you can place them anywhere you want. You also need to have a JRE version 7 or newer to run the IDE. If you are using Ubuntu, you can install it by entering the following command:

```

sudo apt-get install openjdk-7-jre-headless

```

You also need access to serial ports. Again on Ubuntu, you can use the following to add yourself to the dialout group to get permission:

```

sudo usermod -a -G dialout `whoami`

```

In the Linux Mojo IDE files, there is a folder named *driver* with a file 99-mojo.rules. You should copy this file to /etc/udev/rules.d/. This ensures that you have permission to connect to the Mojo and prevents Ubuntu from thinking it is a modem and locking it up for a while whenever it is plugged in.

You should log out or restart your computer to make sure all these changes take effect.

# **Mojo IDE Settings**

Before you create your first project, you need to tell the Mojo IDE where you installed ISE and what serial port the Mojo connects to.

Launch the Mojo IDE. If you installed it using the Windows installer, you should have a Start Menu entry and/or a desktop icon that you can use to launch it. If you downloaded the Windows files, you can double-click the *mojo-ide.exe* file after extracting the archive. On Linux, you need to run the *mojo-ide* script. This can be done with the following command:

```

./mojo-ide

```

You will be greeted by a welcome dialog box that has a little info about the version of the IDE you downloaded. You can get this welcome dialog back by going to Help  $\rightarrow$ About Mojo IDE.

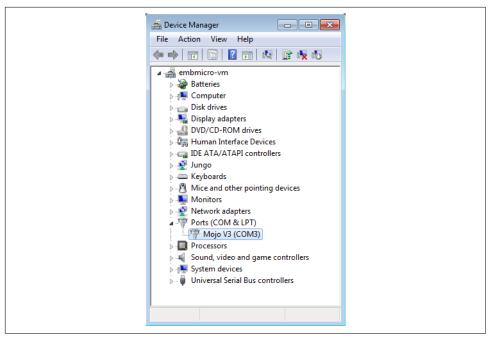

Go ahead and plug in the Mojo if you haven't already. You need to figure out what serial port the Mojo is connected to. On Windows, you need to open the Device Manager. Launch the Control Panel and navigate to Hardware and Sound. You should then see Device Manager under Devices and Printers.

In the Device Manager, expand Ports (COM & LPT). You should see an entry such as Mojo V3 (COM3), as shown in Figure 1-12. The number following COM may be different. This is the port it is connected to. Remember this.

Figure 1-12. The Mojo is connected to COM3. The COM port number may be different for you.

On Linux, the Mojo will most likely connect to /dev/ttyACM0 or /dev/ttyUSB0. If you have more than one USB-to-serial device, the last number may be nonzero. You can list the ports on your computer with the following command:

ls /dev/tty\*

If you unplug the Mojo and list the ports, and then plug it back in and list them again, the new one is what the Mojo is connected to.

Back in the Mojo IDE, open the Serial Port Selector by going to Settings  $\rightarrow$  Serial Port and select the correct serial port, as shown in Figure 1-13.

Figure 1-13. Select the serial port you found in the preceding step

The last step is to tell the IDE where to find the Xilinx tools. If you installed them in the default location,  $C:\Xilinx\14.7$  on Windows or  $\/opt/Xilinx/14.7$  on Linux, then

you can skip this step because the IDE will check these by default. Otherwise, go to Settings  $\rightarrow$  ISE Location and locate the *14.7* directory in your installation.

Everything should now be good to go! It's time to start your first project.

# **Your First FPGA Project**

Now that everything is set up, we are going to create a basic design that will turn on an LED when you press a button. Although this is a fairly trivial example, it presents a lot of new things that will take some time to understand.

# **Creating a New Project**

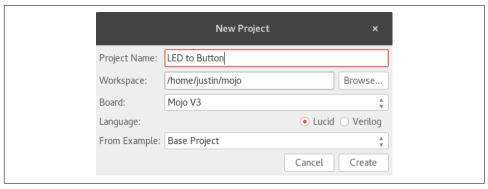

In the Mojo IDE, choose File  $\rightarrow$  New Project to open the New Project dialog box, shown in Figure 2-1.

Figure 2-1. Creating a new project

You can make the project name whatever you want, but "LED to Button" fits well. The *Workspace* is the directory where all your projects will be created. In this example, the new project will be in /home/justin/mojo/LED to Button. Note that if you are using Windows, your path will look different. Make sure Lucid is selected for the language. The From Example option sets what your new project will be based on. There is no fully blank project because there are a lot of connections to the FPGA internal to

the Mojo that you always want to have defined. The Base Project is the most basic template and does nothing except provide a boilerplate design.

Click the Create button to create a new project.

Your project should be created and opened. In the left project tree, expand the project, and then expand Source and double-click *mojo\_top.luc*, as shown in Figure 2-2.

```

| Mognible Version Blaid | Mognible Version Bl

```

Figure 2-2. New project with mojo\_top.luc open

Notice that the name of the open tab is yellow and some of the lines have yellow highlighting. These represent warnings. If you hover your cursor over one, a tooltip will pop up, telling you the actual warning. In this case, these are all warnings about unused inputs. You can also click the little checkbox icon in the toolbar to run a check on your design, and all the warnings and errors will be printed to the console.

# **Understanding Modules**

Hardware designs are broken into modules. This is similar to how programs are broken down into functions. A module is a circuit with a set of inputs and outputs. In this example, we have only one module called mojo top. This is the top-level module of our project. That means that all the inputs and outputs to the module are actual inputs and outputs of the FPGA instead of internal signals. Later we will instantiate modules inside the top-level module, and all their inputs and outputs will be internal to the FPGA.

Take a look at the port declarations. These are all the connections internal to the Mojo. For this project, we care only about rst\_n and led. Besides clk (which is covered later), all the other ports connect to the microcontroller on the Mojo. Note that microcontroller is an AVR (ATmega32U4), and the avr prefix on some of the port names refers to this. The connections to the AVR are used to give the FPGA access to the USB port as well as the analog inputs. The n of rst n is there to indicate that it is active low: when the button is pressed, it will have a value of 0 (active), and when the button is just sitting, it will have a value of 1 (inactive):

```

module mojo_top (

input clk,

// 50MHz clock

// reset button (active low)

input rst n,

input spi_ss,

// AVR SPI Slave Select

input spi_mosi, // AVR SPI MOSI

input spi_sck, // AVR SPI Clock

// AVR SPI Clock

output spi_channel [4], // AVR general purpose pins

// (used by default to select ADC channel)

// AVR TX (FPGA RX)

input avr_tx,

output avr_rx,

input avr_rx_busy

{

// AVR RX (FPGA TX)

// AVR RX buffer full

```

There are three types of ports: input, output, and inout. By far the most common are inputs and outputs. These are unidirectional and are fairly straightforward to use. Inouts, on the other hand, are bidirectional. Outputs, like inouts, can be tri-stated (output driver is disabled). However, output values can never be read. FPGAs don't have a way to have an internal signal be bidirectional, so inouts can be routed only directly out of the FPGA. Again, this is covered later.

In the FPGA, we call all of these *signals*. It is similar in concept to a variable in code, but they are actual wires carrying signals instead of a value in memory. Signals in a design are a single bit wide unless you specify them to be an array. The output led is an example of this. The [8] that comes after the name specifies that it is 8 bits wide. Each bit of the array corresponds to an LED on the Mojo.

One of the major benefits to breaking your design into modules is that you can reuse them. What makes this really powerful is the use of parameters. This example doesn't show it, but a module declaration can have a parameter list. These are constants that can be set when the module is instantiated and that allow you to write a generic module that can be customized for each situation.

# Representing Values

Before moving on to the next section, let's take a minor detour into how values are represented in Lucid. Values are represented using one or more bits. The number of bits a value has is known as its *width*. There are a few ways to specify a value. Some of them allow you to specify a width, while others use an implied width.

The most basic way to represent a value is with a simple number such as 9. When you do this, the width will be the minimum number of bits needed to represent that value.

Sometimes it's easier to specify a number with a different radix (base) than 10. Lucid supports decimal, binary, and hexadecimal. To specify the radix, prefix the value with d, b, or h for decimal, binary, and hexadecimal, respectively. For example, hFF has the decimal value 255, and b100 has the decimal value 4. If you don't append a radix indicator, decimal is assumed.

It is important to remember that all numbers will be represented as bits in your circuit. When you specify a number this way, the width of the number will be the minimum number of bits required to represent that value when using decimal. For binary, it is simply the number of digits; for hexadecimal, it is four times the number of digits. For example, the value 7 will be 3 bits wide (111), 1010 will be 4 bits wide, and hACB will be 12 bits wide.

You will usually want to specify exactly how many bits a value should be. To do this, you prefix the radix letter with the number of bits. For example, 4d2 will be the value 2, but using 4 bits instead of the minimum 2 (binary value 0010 instead of 10). You must specify the radix when specifying the width to separate the width from the value.

If you specify a width smaller than the minimum number of bits required, the number will drop the most significant bits. When this happens, you will get a warning.

Table 2-1 shows different ways to represent the same values.

*Table 2-1. Value representations*

| Decimal           | Hex       | Binary                        |

|-------------------|-----------|-------------------------------|

| 6 or d6 or 3d6    | 3h6       | b110 or 3b110                 |

| 15 or d15 or 4d15 | hF or 4hF | b1111 or 4b1111               |

| 6d12              | 6hC       | b001100 or 6b001100 or 6b1100 |

Although all signals in your design will have a value of 0 or 1, you can assign two other values. One is x, which generally means don't care. It means you want to assign a value, but you don't care what value gets assigned. Why would you do this instead of just assigning something random? By assigning x, you give the tools the flexibility to select whatever value is most convenient. It may turn out that assigning a value of 1 makes your design much simpler to realize in hardware, and since you don't care, the tools can use that.

The x value will also show up in simulations, and in that case it means the value is unknown. Either something wasn't initialized properly or some of your don't care values are floating around. This is another reason to use x when you don't think you care about a value. When you simulate, the unknown values will propagate if used (for example, x + 2 = x), so you can ensure that the value really doesn't matter.

The last value is z, which means high-impedance. Assigning z means you are effectively disconnecting that signal. It's important to know that FPGAs can't realize highimpedance signals internally. This means the only time you should use z is for outputs of the top module (the module that connects to physical I/O pins). The only real use of z is to disable outputs. This is useful for creating an open collector output (instead of 0 and 1, you use 0 and z) or for disabling pins that may be driven externally.

# **Using Always Blocks**

Let's skip to the always block. We will return to the lines before it shortly.

These blocks are where all the magic happens. They are where you can perform computation and read/write signals. The always block gets its name because it is always happening. When the tools see an always block, they need to generate a digital circuit that will replicate the *behavior* that the block describes.

Both Verilog and VHDL have their versions of the always block. In Verilog, they are also called always blocks. In VHDL, they are called processes.

Take a look at the always block in this example:

```

alwavs {

reset_cond.in = ~rst_n; // input raw inverted reset signal

rst = reset_cond.out; // conditioned reset

led = 8h00;  // turn LEDs off

spi_miso = bz;  // not using SPI

spi_channel = bzzzz; // not using flags

avr_rx = bz; // not using serial port

```

The always block is an abstraction that allows us to create complicated designs without having to worry about exactly how it will be implemented. Inside an always block, statements that appear lower in the block have priority over earlier statements. This is kind of similar to programming, where if you write to a variable twice, the second write will be the one that persists, but this is just an abstraction. If a value is written twice in an always block, it is as if the first line doesn't even exist. Take a look at the following example:

```

always {

led = 8h00:

// turn LEDs off

led = 8hFF;

// turn LEDs on

}

```

So what happens when this is synthesized? If you are thinking about this as code, you may be tempted to think that the LEDs would turn on and off continuously, but that's not what happens. Remember, there is no processor running code; instead, a circuit will be made from this block. When the tools synthesize this, the first line will be ignored completely, and the LEDs will always be on. The led output would be hardwired high. Although this example is trivial, and you would never write to the same signal sequentially like this, with conditional assignments (such as if statements) this becomes important.

Back to our design, the always block assigns values to six signals. Every output in a module must be assigned a value in all circumstances. Because the base project does nothing, and these signals are unused, they are assigned reasonable defaults.

Look at the first two lines in the always block:

```

reset_cond.in = ~rst_n; // input raw inverted reset signal

rst = reset_cond.out; // conditioned reset

```

On the first line, we are assigning a value to the input in of the module reset\_cond. Modules, such as reset cond, can be used inside other modules. This is similar to how you can call functions from other functions in code. However, unlike code, where you reuse the exact same instructions, the module will be duplicated in hardware each time you use it. This is why when you use a module it is called *instantiating* that module. You are creating another instance of it. We will get into more detail

about how to instantiate a module in the next section, so don't worry about these lines too much.

We are trying to connect the rst n input, which corresponds to the reset button on the board, to reset\_cond.in. Note that we actually connect ~rst\_n to the input. The ~ operator inverts the signal (1 becomes 0, and 0 becomes 1). This makes it active high (1 means the button is pressed) instead of active low.

The second line connects the output out of reset\_cond to the signal rst. The importance of reset cond will become clear later, but for now just know that it cleans up (synchronizes it to clk) the button input, and rst will be 1 when the reset button is pressed and 0 when it isn't. For this simple example, it isn't needed, and we could use the rst n input directly.

Take a look at the last four lines now:

```

led = 8h00:

// turn LEDs off

avr rx = bz;

// not using serial port

```

On the first line, we assign the led output to all 0s. Remember from the port declaration that led is 8 bits wide. On this line we use 8h00 to make it clear we are setting all 8 bits to 0. We could have also just used the value 0. This is because 0 would become 1d0, but since led is 8 bits wide, it would be padded with 0s to match the width and would become equivalent to 8b00000000 (or 8h00).

The next three lines are assigning z to the signals. This is because these signals are outputs, so they need a value, but we aren't using them in this example. Since they aren't being used, the safest value is z. These signals connect to the microcontroller on the Mojo and are used to get access to the USB port and analog inputs.

When using x or z, constants won't be padded with 0. For example, if you assign bx to a 4-bit signal, it will expand to 4bxxxx and not 4b000x. This is true only if the most significant bit is x or z. If you assign b0x to a 4-bit signal, it will expand to 4b000x.

If you look at the full always block, you'll notice that there are no redundant assignments. When the design is synthesized, these values will be hardwired to the signals. The led output will be tied low, and the other outputs will be left floating (high impedance).

## Connecting the Button

We are going to modify the module to connect the reset button to the first LED so that when you push the button, the LED turns on.

The output led is 8 bits wide. Each one of these bits corresponds to a single LED on the board. The least significant bit connects to the topmost LED (rightmost when the LED side of the board is facing you). Arrays in hardware are nothing more than a collection of single-bit signals and are really just a way to conveniently group (and do math on) related bits.

Since led is 8 bits wide, we need to assign an 8-bit array to it (each bit needs a value). However, the signal rst is a single bit wide. To compensate, we use the *concatenation* operator.

To concatenate multiple arrays into a single larger one, you can use the concatenation operator that takes the form  $c\{x, y, z\}$ . Here the arrays (or single-bit values) x, y, and z will be concatenated into a single larger array.

We can modify line 28 to concatenate 7h00, which is seven zeros, with rst, which is a single bit wide, to create an 8-bit array with the 7 most significant bits 0 and the leastsignificant bit connected to rst:

```

led = c{7h00, rst}; // connect rst to the first LED

```

## **Building Your Project**

Go ahead and click the little hammer icon in the toolbar to build your project. As the project builds, you should see a bunch of text printed in the console. Just wait for it to finish building. It should look like Figure 2-3.

The important line here is impl 1 finished. This means your project was built without errors. If you are using Lucid, the Mojo IDE should catch any syntax/design errors. However, as your projects get more advanced, it is possible to create designs that can't be realized in the FPGA, and you will need to check the build output for what went wrong.

```

Moio IDE Version B1.3.2

File Project Tools Settings Help

// SOMHz clock

// reset button (active low)

// 8 user controllable LEDs

// configuration clock, AVR ready when high

// AVR SPI MISO

// AVR SPI Slave Select

// AVR SPI Slave Select

// AVR SPI Clock

// AVR SPI Clock

// AVR SPI Clock

// AVR SPI Clock

// AVR TX (FPCA RX)

// AVR TX (FPCA RX)

// AVR RX buffer full

▼ Source

▶ Constraints

t spi_channel [4],

avr tx,

.clk(clk) {

// The reset conditioner is used to synchronize the reset signal to the FPGA

// clock. This ensures the entire FPGA comes out of reset at the same time.

reset_conditioner reset_cond;

reset_cond.in = ~rst_n; // input raw inverted reset signal

rst = reset cond.out; // conditioned reset

"mojo_top_6" is an NCD, version 3.2, device xc6slx9, package tqg144, speed -2

Successfully converted design 'mojo_top_e_routed.ncd' to 'mojo_top_e_routed.xdl'.

Running bitgen with args mojo_top_0_routed.ncd mojo_top_0.bit mojo_top_0.pcf -g Binary:Yes -g Compress -w -intstyle pa

[Non Jun 13 09:36:43 2016] Impl 1 finished

IMFO: [Common 17-266] Exiting PlanAhead at Mon Jun 13 09:36:43 2016...

IMFO: [Common 17-83] Releasing License: PlanAhead

Finished building project.

```

Figure 2-3. Built project with rst connected to led

## **Loading Your Project**

Once your project is built, plug your Mojo into your computer if you haven't already. Also make sure the correct serial port is selected under Settings  $\rightarrow$  Serial Port.

You have two options when programming the Mojo. The first is to load the design directly to the FPGA. This can be done by clicking the hollow arrow icon in the toolbar. FPGAs are RAM-based devices, which means each time they lose power, they also lose their configuration. By loading your design directly to the FPGA, it'll be lost when you disconnect power.

The second option is to program the flash on the Mojo. This will store your design in persistent memory. When the board is powered up, the microcontroller will automatically reconfigure the FPGA. Note that if you program the flash, the microcontroller will program the FPGA at the same time too.

If you have a design loaded in flash and then program the FPGA, when you power cycle the board, the old design in flash will be loaded. This can be helpful if you want to test a design temporarily.

You can also clear the flash by clicking the eraser icon. This will prevent the FPGA from being programmed at power up.

For now, click the hollow arrow to program the FPGA directly, since we will be making some modification soon anyway. After the FPGA is programmed, the IDE should look like Figure 2-4.

```

File Project Tools Settings Help

■ ■ ■ ✓ → ★ ↓ ↓ ◆

▼ LED to Button

▼ Source

mojo_top_luc

L components

► Constraints

■ Constraints

■

```

Figure 2-4. Loading the project directly onto the FPGA

If you look at your Mojo, you should now see the *DONE* LED lit. This LED means that the FPGA was successfully configured (Figure 2-5).

Figure 2-5. Mojo successfully configured

Now push the reset button. The first LED turns on, as shown in Figure 2-6.

Figure 2-6. The first LED turns on when the reset button is pressed

### Some Notes on Hardware

When you press the button, how long does it take for the LED to turn on? If this was a processor instead of an FPGA, the processor would be in a loop reading the button state and turning the LED on or off based on that state. The amount of time between pressing the button and the LED turning on would vary depending on the code the processor was executing and the time it takes to get back to reading the button and turning on the LED. As you add more code to your loop, the variation in delay increases.

However, an FPGA is different. With this design (design, not code), the button input is directly connected to the LED output. You can imagine a physical wire bridging the input to the output inside the FPGA. In reality, it's not a wire but a set of switches (multiplexers) that are set to route the signal directly to the output. Well, this is only partially true, since reset conditioner is there, which does some stuff to clean up the reset signal.

Because the signal doesn't have to wait for a processor to read it, it will travel as fast as possible through the silicon to light the LED. This is almost instant (again, forget about reset\_conditioner)! The best part is that if you wire the button to the LED then go on to create some crazy designs with the rest of the FPGA; the speed of this operation will not decrease. This is because the circuits will operate independently as they both simply exist. It is this parallelism that gives FPGAs their real power.

## **Duplication**

What if we want all the LEDs to turn on and off with the press of the button instead of just one? Well, we could do it by using the concatenation operator as before, but just use rst for each bit:

```

led = c{rst, rst, rst, rst, rst, rst, rst, rst};

```

This is pretty ugly, and there is a much cleaner way to write this. Instead, we can use the duplication operator that takes the form  $M \times \{A\}$ . Here M is the number of times to duplicate *A*. Note that *M* must be a constant. Using this, we can rewrite the line:

```

led = 8x{rst};

```

This line does exactly the same thing as before; it is just a lot cleaner.

## **Array Indexing**

There is another way to write the design so that only one LED turns on. This is by indexing the individual bits in led:

```

led[7:1] = 7h0;

// turn these LEDs off

led[0] = rst;

// connect rst to led[0]

```

The first line uses a multibit selector, [7:1]. You should read this as "seven down-to one," and it selects the bits 7 through 1. Note that the first value, when using this selector, must be equal to or greater than the second value. Both values must also be constants. These 7 bits are then set to 0.

The second line uses the single-bit selector, [0]. This is simply selecting the bit 0, which is then connected to rst.

There is another way to select multiple bits. That is by using the *start-width* selector. When using this selector, instead of specifying the start and stop bits (inclusive) as before, you specify the start bit and the number of bits to include above or below it.

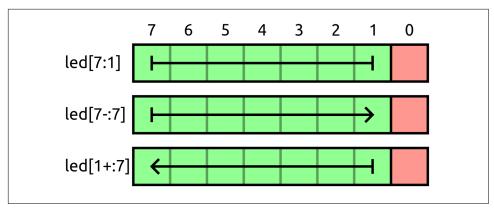

The first line from before could be rewritten in any of these three ways, which are depicted in Figure 2-7:

```

led[7:1] = 7b0; // select bits 7-1

led[7-:7] = 7b0; // select 7 bits starting from 7 and going down

led[1+:7] = 7b0; // select 7 bits starting from 1 and going up

```

*Figure 2-7. Visual of the bit selectors*

The main benefit to using the start-width selector is that the start bit can be dynamically specified by a signal. For example, we could use the value of some switch inputs as the start index instead of a constant number. This is because the width of the selection is guaranteed to be fixed (as the width value must be constant) so that it can be realized in hardware.

## **Always Block Priority**

Because of the nature of always blocks, you could also write the assignment as follows:

```

led = 8b0:

// turn the LEDs off

led[0] = rst;

// connect rst to led[0]

```

As you may remember, the later assignment to led has priority over the earlier one. However, the second assignment assigns only the first bit, so the other seven still retain their values from the first assignment.

Because of the way always blocks work, bit 0 of led will never have the value 0 and will be directly connected to rst. This will create a circuit that is identical to the one before.

Congratulations! You've completed your first FPGA project!

# **Combinational Logic**

Digital circuits can be broken into two main categories: combinational logic and sequential logic (sometimes referred to as *synchronous logic*).

Combinational logic is a digital circuit whose output depends only on the current inputs. The circuit has no memory or feedback loops. It is important to have a strong understanding of combinational logic before proceeding to sequential logic. Even in sequential circuits, you can isolate large sections of combinational logic that perform all the interesting computation.

An example of a combinational logic circuit is the previous button example. The output, if the LED is on, depends only on the current input, if the button is pressed. Another example is a circuit that takes two numbers and adds them together. The output depends only on the two numbers being added. A circuit that would not be considered combinational logic is one that keeps a running total of a series of numbers, as this requires the circuit to remember the current total.

In this chapter, we will run through several combinational logic examples including basic logic gates, various operators, math functions, and more-complex but common circuits. These form the building blocks for all future designs.

### 10 Shield

The next section requires the IO Shield, shown in Figure 3-1. Alternatively, you could set up a comparable circuit on a breadboard. Go to Embedded Micro for the schematic of the IO Shield. We will be using the DIP switches and LEDs to demonstrate combinational circuits.

Figure 3-1. IO Shield

We need to make a new project, but this time we are going to base it on the IO Shield Base example project, instead of the Base Project as before. To do this, go to File  $\rightarrow$ New Project, enter whatever name you want ("IO Shield Demo" is a solid choice) and select IO Shield Base from the From Example drop-down menu.

If you open mojo\_top.luc, you'll notice it is a little different from the version in the bare-bones Base Project we used earlier. We now have some new inputs and outputs declared, and we assign some default values in the always block to them. Take a look at the full module, and after we will dive into the details:

```

module mojo_top (

// 50MHz clock

input clk,

input rst n,

// reset button (active low)

output led [8],

// 8 user controllable LEDs

// configuration clock, AVR ready when high

input cclk,

output spi_miso,

// AVR SPI MISO

input spi_ss,

// AVR SPI Slave Select

input spi_mosi,

// AVR SPI MOSI

// AVR SPI Clock

input spi_sck,

output spi channel [4], // AVR general purpose pins

```

```

// (used by default to select ADC channel)

input avr tx,

// AVR TX (FPGA RX)

output avr_rx,

// AVR RX (FPGA TX)

// AVR RX buffer full

input avr rx busy,

output io led [3][8], // LEDs on IO Shield

output io_seg [8],

// 7-segment LEDs on IO Shield

// Digit select on IO Shield

output io_sel [4],

input io_button [5], // 5 buttons on IO Shield

input io_dip [3][8]

// DIP switches on IO Shield

sig rst;

// reset signal

.clk(clk) {

// The reset conditioner is used to synchronize the reset signal to the FPGA

// clock. This ensures the entire FPGA comes out of reset at the same time.

reset_conditioner reset_cond;

}

always {

reset_cond.in = ~rst_n; // input raw inverted reset signal

rst = reset cond.out; // conditioned reset

led = 8h00;

// turn LEDs off

spi_miso = bz;

// not using SPI

spi_channel = bzzzz; // not using flags

avr_rx = bz;

// not using serial port

io_led = 3x\{8h00\}\}; // turn LEDs off

io seg = 8hff;

// turn segments off

io_sel = 4hf;

// select no digits

}

}

```

If you take a look at where io\_led is declared, you will notice that it is a twodimensional array. This corresponds to the three groups of eight LEDs on the IO Shield:

```

output io_led [3][8], // LEDs on IO Shield

```

In Lucid, you can have multidimensional arrays that can then be indexed into smaller-dimensional arrays or single bits. For example, to led[0] would select the first 8-bit single-dimensional array.

Because to led is multidimensional, we have to use fancy syntax to assign 0 to all of its bits:

```

io_led = 3x\{\{8h00\}\};

// turn LEDs off

```

The first part of this should seem familiar, as it's the duplication syntax from "Duplication" on page 30. But unlike before, we need to create a 3 x 8 array. If we instead wrote 3x{8h00}, that would create a 24-bit single-dimensional array of all 0s. We

need to turn the 8h00 from an 8-bit array into a 1 x 8 array. To do this, we use the array builder operator, which has the form {A, B, C}. Here A, B, and C must all have equal dimensions. For example, {8h00, 8h37, 8hfa} would be valid (and would make a 3 x 8 sized array) but {8h24, 16h2737, 8hfa} would not be.

The value {8h00} then is a 1 x 8 array. By using the duplication operator, we duplicate the outermost dimension, making a 3 x 8 array. We could have also written {8h00, 8h00, 8h00}, but the duplication syntax is a little cleaner.

As you may have noticed, the IO Shield has three groups of eight LEDs. The first dimension of io\_led selects the group, and the second dimension selects the individual LED.

The 2D array io\_dip is organized the sameway as io\_led.

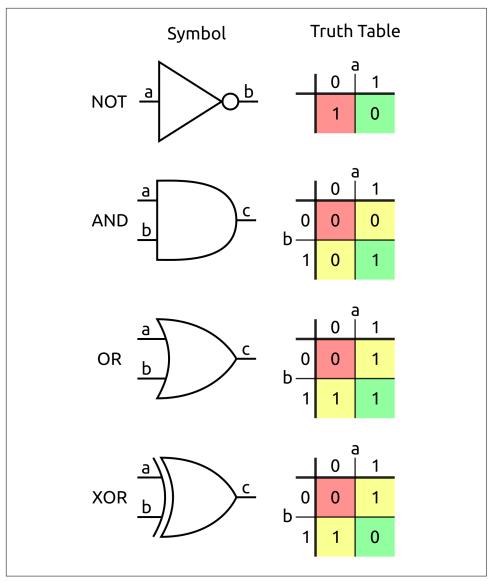

## **Logic Functions**

The first example we will work through is to connect two of the DIP switches to an LED through a logic gate. A *logic gate* is a circuit that takes numerous logical inputs (true/false) and has a single output. In digital circuits, 1 is considered to be true, and 0 is considered to be false. The basic logic gates are NOT, AND, OR, and XOR, which are illustrated in Figure 3-2.

NOT takes a single input, and outputs true only when the input is false. In other words, it negates the input.

AND takes two or more inputs, and outputs true only when all the inputs are true. If an AND gate has two inputs, you can think of its output as being true only if the first input *and* the second input are true.

OR takes two or more inputs, and outputs true only if one or more of the inputs are true. If an OR gate has two inputs, you can think of its output as being true if either the first input *or* the second input is true.

XOR takes two or more inputs, and outputs true only when an odd number of inputs are true. This is a little weird for more than two inputs, but if you look at the twoinput case, it will output true when either input is true, but not when both are true. XOR is short for exclusive or.

There are also variations on AND, OR, and XOR that invert the output. They are known as NAND, NOR, and XNOR, respectively. You can think of them as the base versions followed by a NOT. Their symbols are the same as their parent symbols but with a bubble at the output (like the NOT symbol).

Figure 3-2. Schematic symbols and truth tables for NOT, AND, OR, and XOR

We can add a single line to the end of the always block to turn on the first LED when switch 0 and 1 are both on. Note that we are going to consider the order of the switches from right to left, not left to right as printed on the switches themselves. The rightmost switch in a group is switch 0, and the leftmost is switch 7, as shown in Figure 3-3.

Figure 3-3. IO Shield switch numbering

```

always {

reset_cond.in = ~rst_n; // input raw inverted reset signal

rst = reset cond.out; // conditioned reset

led = 8h00:

// turn LEDs off

spi miso = bz;

// not using SPI

spi channel = bzzzz; // not using flags

avr rx = bz;

// not using serial port

io_led = 3x{{8h00}};

// turn LEDs off

io_seg = 8hff;

// turn segments off

io_sel = 4hf;

// select no digits

io_led[0][0] = io_dip[0][0] & io_dip[0][1]; // new line!

```

Looking at the new line, we need to index the first LED. To do this, we first select the first group, group 0, and the LED is the first in the group, so also index 0. The bit selection is then [0][0]. We index the first and second DIP switches in the same manner. Finally, we use &, the bitwise AND operator, to AND the bits together.

Notice that the line where all of io\_led is assigned to 0 is still the same. Trying to assign all the bits but the first would be overly complicated when the new line will simply override the value for the first bit. It is pretty common to have a line early on in the always block that assigns a default value.

Build and load the project onto your Mojo. Try playing with the rightmost two switches. If either switch is off, the LED will be off. Only when both are on, the LED should be on.

Go back and replace the & operator with the operators for OR and XOR: | and ^. Play with the switches, and make sure you understand how each works.

#### **Practice**

Add two more lines to the always block so that the first LED of the first group lights up as before, the first LED of the second group lights up when either (OR) of the first two switches in the second group are on, and the first LED of the last group lights up only when exactly one (XOR) switch of the first two switches in the last group are on.

## **Bitwise Operators**

So far, all the operators we have talked about are bit-wise operators: they can be used on two equally sized arrays, and they will perform their operation on each pair of bits individually.

For example, if we want to light up an LED in the first group only when the corresponding switch in the first and second groups are both on, we could do the following:

```

io_led[0] = io_dip[0] & io_dip[1];

```

Remember that io\_led[0] is actually an array of 8 bits. The same is true for io\_dip[0] and io\_dip[1]. This single line will create eight AND gates—one for each pair of bits.

You can use the OR and XOR operators in the same way.

We can also chain multiple operators together. For example, if we want the LEDs in the first group to turn on only when the corresponding switches in all three groups are on, we could do the following:

```

io_led[0] = io_dip[0] & io_dip[1] & io_dip[2];

```

Bitwise operators are evaluated from left to right, so in this case io\_dip[0] will be ANDed with io dip[1], and the result of that will be ANDed with io dip[2]. In the case of all AND operators, the order doesn't matter. However, if you start mixing operators, the order can matter. You can use parentheses to force the order you want.

You can negate any of these operators (1 becomes 0, 0 becomes 1) by simply using the ~ operator. This will flip each bit in a single array. If we wanted to NAND the first two groups of switches and output the result on the first group of LEDs, we could use the following:

```

io_led[0] = ~(io_dip[0] & io_dip[1]);

```

### De Morgan's Laws

De Morgan's laws are the pair of Boolean logic relations that allow you to transform between AND and OR operators. The relations are  $\sim (A \Leftrightarrow B) == \sim A \mid \sim B$  and  $\sim (A \mid B) = -A$  &  $\sim B$ . Given this, we could have also written the previous line as follows:

```

io_led[0] = ~io_dip[0] | ~io_dip[1];

```

I would read the original line as "true when io\_dip[0] and io\_dip[1] aren't both on." I would read the second version as "true when either io\_dip[0] or io\_dip[1] are off." However, these are the exact same expressions. You can prove it to yourself with a truth table.

#### Practice

Use two bitwise operators so that the LEDs in the first group light up when the corresponding switch in the third group is on or when both switches in the first two groups are on.

## **Reduction Operators**

The reduction operators are similar to the bitwise operators except they operate on a single array and output a single bit. In other words, they reduce an array to a single bit. You can think of these operators as a single logic gate with as many inputs as the size of the array.

For example, if we wanted to turn the first LED on when all the switches in the first group are on, we could use the following line: