Philippe Coussy Adam Morawiec Editors

# **High-Level Synthesis**

D 1

from Algorithm to Digital Circuit

Foreword by Giovanni De Micheli

# High-Level Synthesis

Philippe Coussy • Adam Morawiec Editors

# High-Level Synthesis

From Algorithm to Digital Circuit

Philippe Coussy Université Européenne de Bretagne - UBS Laboratoire Lab-STICC Centre de Recherche BP 92116 56321 Lorient Cedex France philippe.coussy@univ-ubs.fr Adam Morawiec European Electronic Chips & Systems design Initiative (ECSI) 2 av. de Vignate 38610 Grieres France adam.morawiec@ecsi.org

ISBN 978-1-4020-8587-1 e-ISBN 978-1-4020-8588-8

Library of Congress Control Number: 2008928131

© 2008 Springer Science + Business Media B.V.

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Cover illustration: Cover design by Martine Piazza, Adam Morawiec and Philippe Coussy

Printed on acid-free paper.

9 8 7 6 5 4 3 2 1

springer.com

#### **Foreword**

High-level synthesis – also called behavioral and architectural-level synthesis – is a key design technology to realize systems on chip/package of various kinds, whether single or multi-processors, homogeneous or heterogeneous, for the embedded systems market or not. Actually, as technology progresses and systems become increasingly complex, the use of high-level abstractions and synthesis methods becomes more and more a necessity. Indeed, the productivity of designers increases with the abstraction level, as demonstrated by practices in both the software and hardware domains. The use of high-level models allows designers with systems, rather than circuit, background to be productive, thus matching the trend of industry which is delivering an increasingly larger number of integrated systems as compared to integrated circuits.

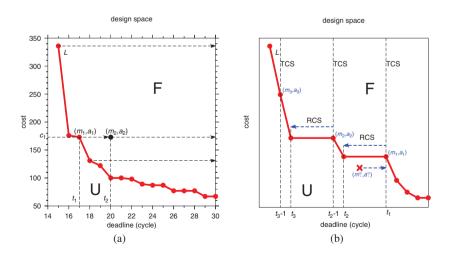

The potentials of high-level synthesis relate to leaving implementation details to the design algorithms and tools, including the ability to determine the precise timing of operations, data transfers, and storage. High-level optimization, coupled with high-level synthesis, can provide designers with the optimal concurrency structure for a data flow and corresponding technological constraints, thus providing the balancing act in the trade-off between latency and resource usage. For complex systems, the design space exploration, i.e., the systematic search for the Pareto-optimal points, can only be done by automated high-level synthesis and optimization tools.

Nevertheless, high-level synthesis has been showing a long gestation period. Despite early results in the 1980s, it is still not common practice in hardware design. The slow acceptance-rate of this important technology has been attributed to a few factors such as designers' desire to micromanage integrated systems by controlling their internal timing and the lack of a universal standard front-end language. The former issue is typical of novel technologies: as systems grow in size it will be necessary for designers to show a broader system vision and fewer concerns on internal timing. In other words, this problem will naturally disappear.

The Babel of high-level modeling languages has been a significant obstacle to the development of this technology. When high-level synthesis was introduced in the 1980s, the designer community embraced Verilog and VHDL as specification languages, due to their ability to perform efficient simulation. Nevertheless,

vi Foreword

such languages were conceived without an intrinsic hardware semantics, making synthesis more cumbersome.

C-based hardware description languages (CHDLs) surfaced in the 1980s as well, such as HardwareC and its hardware compiler Hercules. The limitations of HardwareC and similar CHDLs are rooted in the modification of the C language semantics to support hardware constructs, thus making each CHDL a different dialect of C. The introduction of SystemC in the 1990s solved the problem by not modifying the software programming language (in this case C++) and by introducing a class library with a well-defined hardware semantics. It is regrettable that the initial enthusiasm was mitigated by the limited support of high-level synthesis for SystemC.

The turn of the century was characterized by a renewed interest in CHDLs and in high-level synthesis from CHDLs. New companies carried the torch of educating designers with new models and tools for design. Today, there are several offers in high-level synthesis tools that provide effective solutions in silicon. Moreover, some of the technical roadblocks to high-level synthesis have been overcome. Synthesis of C-based models with pointers and memory allocators was demonstrated and patented by Stanford jointly with NEC, thus removing the last hard technical difficulty to synthesize full C-based models.

At present, the potentials of high-level synthesis are still very good, even though the designers' community has not yet converged on a single modeling language that would lower the entry barrier of tools into the marketplace. This book presents an excellent collection of contributions addressing different aspects of high-level synthesis from both industry and academia. This book should be on each designer's and CAD developer's shelf, as well as on those of project managers who will soon embrace high-level design and synthesis for all aspects of digital system design.

EPF Lausanne, 2008

Giovanni De Micheli

### **Contents**

| 1  | Pascal Urard, Joonhwan Yi, Hyukmin Kwon, and Alexandre Gouraud                                     |

|----|----------------------------------------------------------------------------------------------------|

| 2  | <b>High-Level Synthesis: A Retrospective</b>                                                       |

| 3  | Catapult Synthesis: A Practical Introduction to Interactive C Synthesis                            |

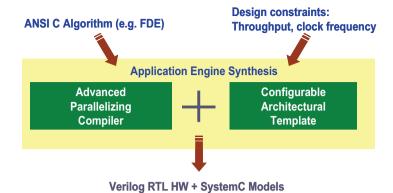

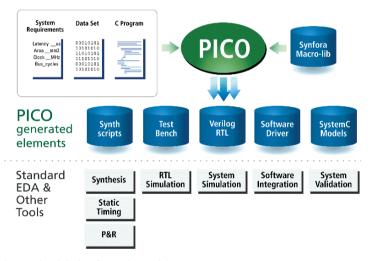

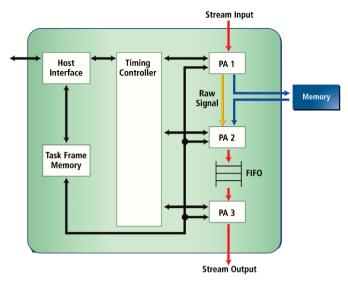

| 4  | Algorithmic Synthesis Using PICO                                                                   |

| 5  | <b>High-Level SystemC Synthesis with Forte's Cynthesizer</b>                                       |

| 6  | AutoPilot: A Platform-Based ESL Synthesis System                                                   |

| 7  | "All-in-C" Behavioral Synthesis and Verification with CyberWorkBench                               |

| 8  | Bluespec: A General-Purpose Approach to High-Level Synthesis Based on Parallel Atomic Transactions |

| 9  | <b>GAUT: A High-Level Synthesis Tool for DSP Applications</b>                                      |

| 10 | User Guided High Level Synthesis                                                                   |

| V111  | Content |

|-------|---------|

| V 111 | Conten  |

| 11 | <b>Synthesis of DSP Algorithms from Infinite Precision Specifications</b> 197 Christos-Savvas Bouganis and George A. Constantinides                        |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12 | <b>High-Level Synthesis of Loops Using the Polyhedral Model</b> 215 Steven Derrien, Sanjay Rajopadhye, Patrice Quinton, and Tanguy Risset                  |

| 13 | <b>Operation Scheduling: Algorithms and Applications</b>                                                                                                   |

| 14 | <b>Exploiting Bit-Level Design Techniques in Behavioural Synthesis</b> 257 María Carmen Molina, Rafael Ruiz-Sautua, José Manuel Mendías, and Román Hermida |

| 15 | High-Level Synthesis Algorithms for Power and Temperature Minimization                                                                                     |

#### **Contributors**

#### Shail Aditya

Synfora, Inc., 2465 Latham Street, Suite #300, Mountain View, CA 94040, USA, shail.aditya@synfora.com

#### Ivan Augé

UPMC-LIP6/SoC, Équipe ASIM/LIP6, Université Pierre et Marie Curie, Paris, France, Ivan.Auge@lip6.fr

#### Thomas Bollaert

Mentor Graphics, 13/15 rue Jeanne Braconnier, 92360 Meudon-la-Foret, France, Thomas\_Bollaert@mentor.com

#### Pierre Bomel

European University of Brittany – UBS, Lab-STICC, BP 92116, 56321 Lorient Cedex, France, pierre.bomel@univ-ubs.fr

#### Christos-Savvas Bouganis

Department of Electrical and Electronic Engineering, Imperial College London, South Kensington Campus, London SW7 2AZ, UK, christos-savvas.bouganis@imperial.ac.uk

#### Forrest Brewer

Electrical and Computer Engineering, University of California, Santa Barbara, CA 93106-9560, USA, forrest@ece.ucsb.edu

#### Cyrille Chavet

European University of Brittany – UBS, Lab-STICC, BP 92116, 56321 Lorient Cedex, France, chavet@univ-ubs.fr

x Contributors

#### Jason Cong

AutoESL Design Technolgoies, Inc., 12100 Wilshire Blvd, Los Angeles, CA 90025, USA

and

UCLA Computer Science Department, Los Angeles, CA 90095-1596, USA, cong@autoesl.com, cong@cs.ucla.edu

#### George A. Constantinides

Department of Electrical and Electronic Engineering, Imperial College London, South Kensington Campus, London SW7 2AZ, UK, george.constantinides@ieee.org

#### Philippe Coussy

European University of Brittany – UBS, Lab-STICC, BP 92116, 56321 Lorient Cedex, France, philippe.coussy@univ-ubs.fr

#### Steven Derrien

Irisa, universit'e de Rennes 1, Campus de beaulieu, 35042 Rennes Cedex, France, steven.derrien@irisa.fr

#### Robert P. Dick

Department of Electrical Engineering and Computer Science, Northwestern University, Evanston, IL, USA, dickrp@northwestern.edu

#### Yiping Fan

AutoESL Design Technolgoies, Inc., 12100 Wilshire Blvd, Los Angeles, CA 90025, USA, fanyp@autoesl.com

#### Wenrui Gong

Department of Electrical and Computer Engineering, University of California, Santa Barbara, CA 93106, USA, gong@ece.ucsb.edu

#### Alexandre Gouraud

France Telecom R&D, 38-40 rue du General Leclerc, 92794 Issy Moulineaux Cedex 9, France, alexandre.gouraud@orange-ftgroup.com

#### Rajesh Gupta

Computer Science and Engineering, University of California, San Diego, 9500 Gilman Drive, La Jolla, CA 92093-0404, USA, rgupta@ucsd.edu

#### Guoling Han

AutoESL Design Technolgoies, Inc., 12100 Wilshire Blvd, Los Angeles, CA 90025, USA, leohgl@autoesl.com

#### Dominique Heller

European University of Brittany – UBS, Lab-STICC, BP 92116, 56321 Lorient Cedex, France, dominique.heller@univ-ubs.fr

Contributors xi

#### Román Hermida

Facultad de Informática, Universidad Complutense de Madrid, c/Prof. José García Santesmases s/n, 28040 Madrid, Spain, rhermida@dacya.ucm.es

#### Niraj K. Jha

Department of Electrical and Engineering, Princeton University, Princeton, NJ 08544, USA, jha@princeton.edu

#### Wei Jiang

AutoESL Design Technolgoies, Inc., 12100 Wilshire Blvd, Los Angeles, CA 90025, USA, wjiang@autoesl.com

#### Ryan Kastner

Department of Electrical and Computer Engineering, University of California, Santa Barbara, CA 93106, USA, kastner@ucsd.edu

#### Vinod Kathail

Synfora, Inc., 2465 Latham Street, Suite # 300, Mountain View, CA 94040, USA, vinod.kathail@synfora.com

#### Hyukmin Kwon

Samsung Electronics Co., Suwon, Kyunggi Province, South Korea, hm25.kwon@samsung.com

#### Eric Martin

European University of Brittany – UBS, Lab-STICC, BP 92116, 56321 Lorient Cedex, France, eric.martin@univ-ubs.fr

#### José Manuel Mendías

Facultad de Informática, Universidad Complutense de Madrid, c/Prof. José García Santesmases s/n, 28040 Madrid, Spain, mendias@dacya.ucm.es

#### Michael Meredith

VP Technical Marketing, Forte Design Systems, San Jose, CA 95112, USA, mmeredith@ForteDS.com

#### María Carmen Molina

Facultad de Informática, Universidad Complutense de Madrid, c/Prof. José García Santesmases s/n, 28040 Madrid, Spain, cmolinap@dacya.ucm.es

#### Rishiyur S. Nikhil

Bluespec, Inc., 14 Spring Street, Waltham, MA 02451, USA, nikhil@bluespec.com

#### Frédéric Pétrot

INPG-TIMA/SLS, 46 Avenue Félix Viallet, 38031 Grenoble Cedex, France, Frederic.Petrot@imag.fr

#### Patrice Quinton

ENS de Cachan, antenne de Bretagne, Campus de Ker Lann, 35 170 Bruz Cedex, France, patrice.quinton@irisa.fr

xii Contributors

#### Sanjay Rajopadhye

Department of Computer Science, Colorado State University, 601 S. Howes St. USC Bldg., Fort Collins, CO 80523-1873, USA, Sanjay.Rajopadhye@colostate.edu

#### Tanguy Risset

CITI – INSA Lyon, 20 avenue Albert Einstein, 69621, Villeurbanne, France, tanguy.risset@insa-lyon.fr

#### Rafael Ruiz-Sautua

Facultad de Informática, Universidad Complutense de Madrid, c/Prof. José García Santesmases s/n, 28040 Madrid, Spain, rsautua@fdi.ucm.es

#### Benjamin Carrion Schafer

EDA R&D Center, Central Research Laboratories, NEC Corp., Kawasaki, Japan, schaferb@bq.jp.nec.com

#### Eric Senn

European University of Brittany – UBS, Lab-STICC, BP 92116, 56321 Lorient Cedex, France, eric.senn@univ-ubs.fr

#### Li Shang

Department of Electrical and Computer Engineering, Queen's University, Kingston, ON, Canada K7L 3N6, li.shang@queensu.ca

#### Pascal Urard

STMicroelectronics, Crolles, France, pascal.urard@st.com

#### Kazutoshi Wakabayashi

EDA R&D Center, Central Research Laboratories, NEC Corp., Kawasaki, Japan, wakaba@bl.jp.nec.com

#### Gang Wang

Technology Innovation Architect, Intuit, Inc., 7535 Torrey Santa Fe Road, San Diego, CA 92129, USA, Gang\_Wang@intuit.com

#### Changqi Yang

AutoESL Design Technolgoies, Inc., 12100 Wilshire Blvd, Los Angeles, CA 90025, USA, charles@autoesl.com

#### Joonhwan Yi

Samsung Electronics Co., Suwon, Kyunggi Province, South Korea, joonhwan.yi@samsung.com, joonhwan.yi@gmail.com

#### Zhiru Zhang

AutoESL Design Technolgoies, Inc., 12100 Wilshire Blvd, Los Angeles, CA 90025, USA, zhiruz@autoesl.com

#### List of Web sites

#### Chapter 2

Microelectronic Embedded Systrems Laboratory at UCSD hosts a number of projects related to system level design, synthesis and verification. Our recent projects include the SPARK parallelizing synthesis framework, SATYA verification framework. Earlier work from the laboratory formed the technical basis for the SystemC initiative. http://mesl.ucsd.edu/

#### Chapter 3

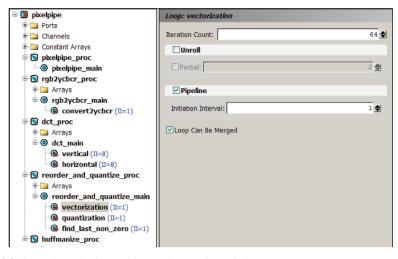

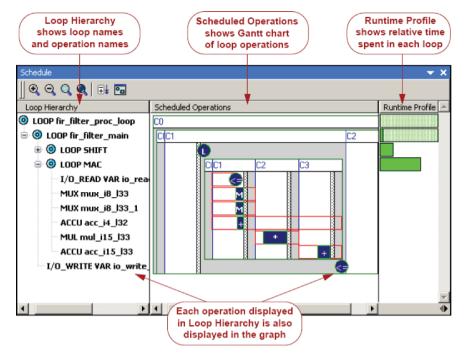

Catapult Synthesis product information page

The home page for Catapult Synthesis on www.mentor.com, with links to product datasheets, free software evaluation, technical publications, success stories, testimonials and related ESL product information.

http://www.mentor.com/products/esl/high\_level\_synthesis/

#### Algorithmic C datatypes download page

The Algorithmic C arbitrary-length bit-accurate integer and fixed-point data types allow designers to easily model bit-accurate behavior in their designs. The data types were designed to approach the speed of plain C integers. It is no longer necessary to compromise on bit-accuracy for the sake of speed or to explicitly code fixed-point behavior using integers in combination with shifts and bit masking.

http://www.mentor.com/products/esl/high\_level\_synthesis/ac\_datatypes

#### Chapter 4

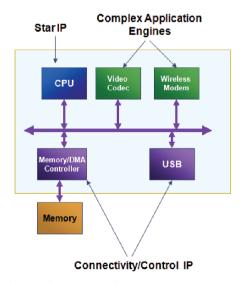

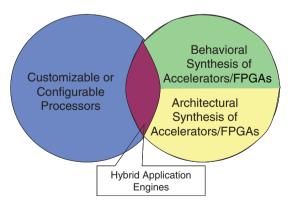

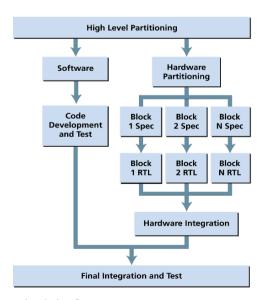

Synfora, Inc. is the premier provider of PICO family of algorithmic synthesis tools to design complex application engines for SoCs and FPGAs. Synfora's technology helps to reduce design costs, dramatically speed IP development and verification,

xiv List of Web sites

and reduce time-to-market. For the latest information on Synfora and PICO products, please visit http://www.synfora.com

#### Chapter 5

More information on Cynthesizer from Forte Design Systems can be found at http://www.ForteDS.com

#### Chapter 6

More information on AutoPilotTM from AutoESL Design Technologies can be found at http://www.autoesl.com and http://cadlab.cs.ucla.edu/soc/

#### Chapter 7

Home Page for CyberWorkBench from NEC http://www.cyberworkbench.com

#### Chapter 8

More information on Bluespec can be found at http://www.bluespec.com Documentation, training materials, discussion forums, inquiries about Bluespec SystemVerilog. http://csg.csail.mit.edu/oshd/

Open source hardware designs done by MIT and Nokia in Bluespec SystemVerilog for H.264 decoder (baseline profile), OFDM transmitter and receiver, 802.11a transmitter, and more.

#### Chapter 9

GAUT is an open source project at UEB-Lab-STICC. The software for this project is freely available for download. It is provided with a graphical user interface, a quick start guide, a user manual and several design examples. GAUT is currently supported on Linux and Windows. GAUT has already been downloaded more than 200 times by people from industry and academia in 36 different countries. For more information, please visit:

http://web.univ-ubs.fr/gaut/

List of Web sites xv

#### Chapter 10

More information can be found on UGH from at UPMC-LIP6/SoC and INPG-TIMA/SLS at http://www-asim.lip6.fr/recherche/disydent/

This web site contains introduction text, source code and tutorials (through CVS) of the opensource Dysident framework that includes the UGH HLS tool.

#### Chapter 11

More information on Chapter 11 can be found at http://cas.ee.ic.ac.uk/

#### Chapter 12

More information on MMAlpha can be found at http://www.irisa.fr/cosi/ALPHA/

#### Chapter 13

More information Chapter 13 can be found on at http://www.cse.ucsd.edu/~ kastner/research/aco/

#### **Chapter 14**

More information on Chapter 14 can be found at http://atc.dacya.ucm.es/

#### **Chapter 15**

More information on Chapter 15 can be found at http://www.princeton.edu/~jha

#### Chapter 1 User Needs

Pascal Urard, Joonhwan Yi, Hyukmin Kwon, and Alexandre Gouraud

Abstract One can see successful adoption in industry of innovative technologies mainly in the cases where they provide acceptable solution to very concrete problems that this industry is facing. High-level synthesis promises to be one of the solutions to cope with the significant increase in the demand for design productivity beyond the state-of-the-art methods and flows. It also offers an unparalleled possibility to explore the design space in an efficient way by dealing with higher abstraction levels and fast implementation ways to prove the feasibility of algorithms and enables optimisation of performances. Beyond the productivity improvement, which is of course very pertinent in the design practice, the system and SoC companies are more and more concerned with their overall capability to design highly complex systems providing sophisticated functions and services. High-level synthesis may considerably contribute to maintain such a design capability in the context of continuously increasing chip manufacturing capacities and ever growing customer demand for function-rich products.

In this chapter three leading industrial users present their expectations with regard to the high-level synthesis technology and the results of their experiments in practical application of currently available HLS tools and flows. The users also draw conclusions on the future directions in which they wish to see the high-level synthesis evolves like multi-clock domain support, block interface synthesis, joint optimisation of the datapath and control logic, integration of automated testing to the generated hardware or efficient taking into account of the target implementation technology for ASICs and FPGAs in the synthesis process.

1

Pascal Urard STMicroelectronics

Joonhwan Yi and Hyukmin Kwon Telecommunication R&D, Samsung Electronics Co., South Korea

Alexandre Gouraud France Telecom R&D P. Urard et al.

**Keywords:** High-level synthesis, Productivity, ESL, ASIC, SoC, FPGA, RTL, ANSI C, C++, SystemC, VHDL, Verilog, Design, Verification, IP, TLM, Design space exploration, Memory, Parallelism, Simulation, Prototyping

# 1.1 System Level Design Evolution and Needs for an IDM Point of View: STMicroelectronics<sup>1</sup>

#### Pascal Urard, STMicroelectronics

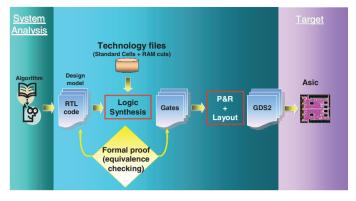

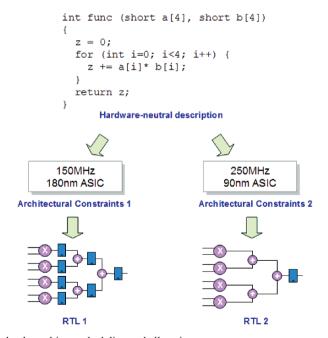

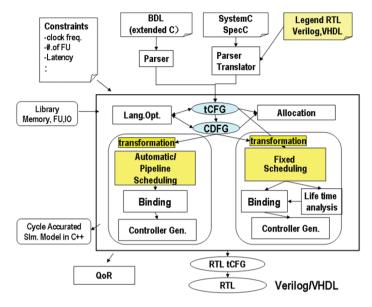

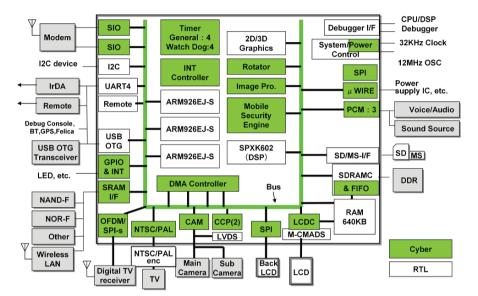

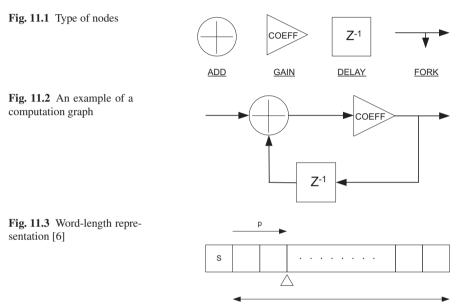

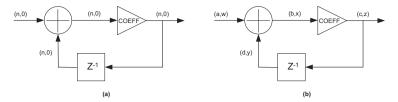

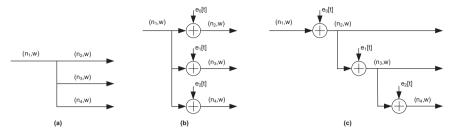

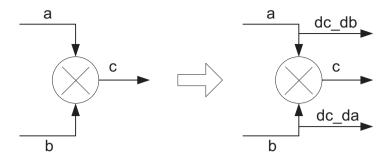

The complexity of digital integrated circuits has always increased from a technology node to another. The designers often had to adapt to the challenge of providing commercially acceptable solution with a reasonable effort. Many evolutions (and sometimes revolutions) occurred in the past: back-end automation or logical synthesis were part of those, enabling new area of innovation. Thanks to the increasing integration factor offered by technology nodes, the complexity in latest SoC has reached tens of millions of gates. Starting with 90 nm and bellow, RTL design flow (Fig. 1.1) now shows its limits.

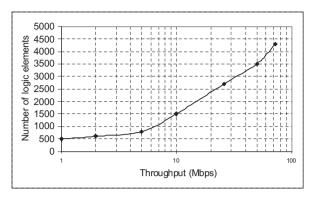

The gap between the productivity per designer and per year and the increasing complexity of the SoC, even taking into account some really conservative number of gates per technology node, lead to an explosion of the manpower for SoCs in the coming technology node (Fig. 1.2).

There is a tremendous need for productivity improvement at design level. This creates an outstanding opportunity for new design techniques to be adopted: designers, facing this challenge, are hunger to progress and open to raise the level of abstraction of the golden reference model they trust.

A new step is needed in productivity. Part of this step could be offered by ESLD: Electronics System Level Design. This includes HW/SW co-design and High-Level Synthesis (HLS).

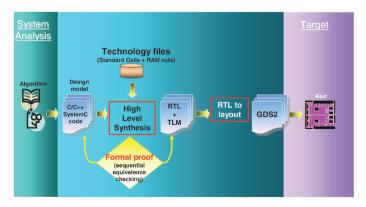

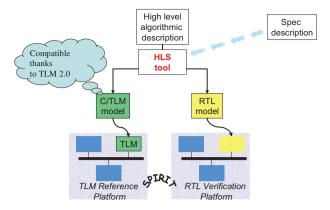

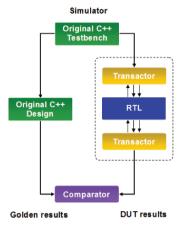

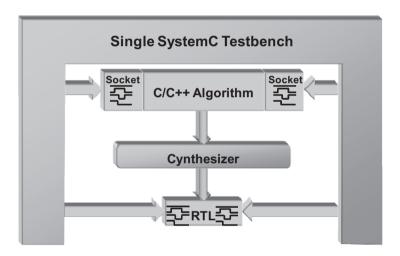

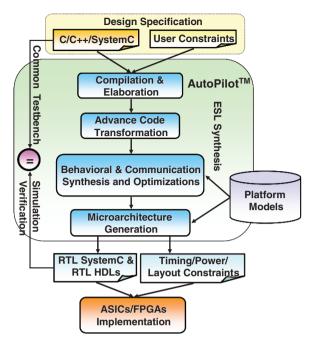

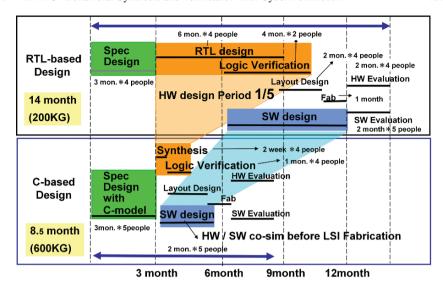

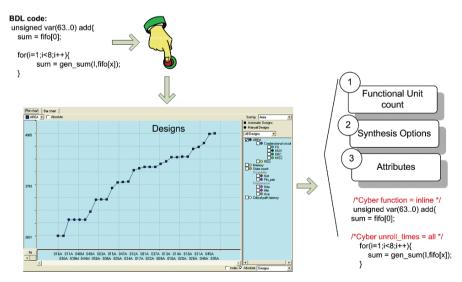

HW/SW co-design deployment has occurred few years ago, thanks to SystemC and TLM coding. HLS however is new and just starting to be deployed. Figure 1.3 shows the basis of STMicroelectronics C-level design methodology. A bit-accurate reference model is described at functional level in C/C++ using SystemC or equivalent datatypes. In the ideal case, this C-level description has to be extensively validated using a C-level testbench, in the functional environment, in order to become the golden model of the implementation flow. This is facilitated by the simulation speed of this C model, usually faster than other kinds of description. Then, taking into account technology constraints, the HLS tool produces an RTL representation, compatible with RTL-to-GDS2 flow. Verification between C-level model and RTL is done either thanks to sequential equivalence checking tools, or by extensive simulations. Started in 2001 with selected CAD-vendors, the research on new flows

<sup>&</sup>lt;sup>1</sup> (C) Pascal Urard, STMicroelectronics Nov. 2006. Extracted for P. Urard presentation at ICCAD, Nov. 2006, San José, California, USA.

1 User Needs 3

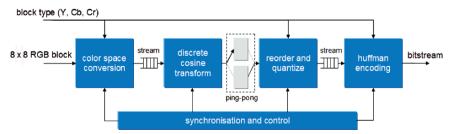

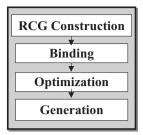

Fig. 1.1 RTL Level design flow

| 1991                       | 1994                                      | 1006 | 1998 | 2000 | 2002 | 2004 | 2006 | 2008 | 2010 |

|----------------------------|-------------------------------------------|------|------|------|------|------|------|------|------|

| 0.7                        | 0.5                                       | 0.35 | 0.25 | 0.18 | 0.13 | 90   | 65   | 45   | 32   |

| 1k                         | 5k                                        | 15k  | 30k  | 45k  | 80k  | 150k | 300k | 600k | 1.2M |

|                            | #Gates / Die (50mm2) conservative numbers |      |      |      |      |      |      |      |      |

| 50K                        | 250K                                      | 750k | 1.5M | 2.2M | 4M   | 7.5M | 15M  | 30M  | 60M  |

|                            | #Gates per Designer per year              |      |      |      |      |      |      |      |      |

| 4k                         | 6k                                        | 9k   | 40k  | 56k  | 91k  | 125k | 200k | 200k | 200k |

| Men / Years per 50 mm2 Die |                                           |      |      |      |      |      |      |      |      |

| ~10                        | ~40                                       | ~80  | ~40  | ~40  | ~43  | ~60  | ~75  | ~150 | ~300 |

→ It is urgent to win some productivity

Fig. 1.2 Design challenges for 65 nm and below

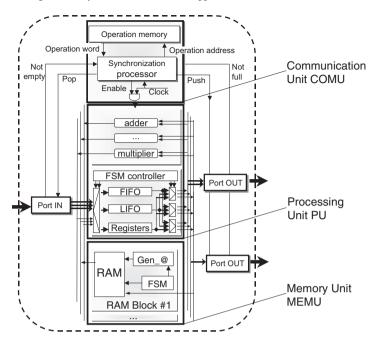

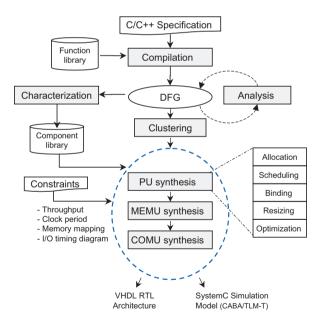

Fig. 1.3 High level synthesis flow

P. Urard et al.

# 10X A % HLS + Formal Proof when reusing HL models 1/2X first trails Design #1 Nesign #2

#### Design Productivity vs Manual RTL (base 1)

Fig. 1.4 Learning curve

has allowed some deployment of HLS tools within STMicroelectronics starting in 2004, with early division adopters. We clearly see in 2007 an acceleration of the demand from designers. Those designers report to win a factor  $\times 5$  to  $\times 10$  in terms of productivity when using C-level design methodology depending on the way they reuse in design their IPs (Fig. 1.4). More promising: designers that moved to C-level design usually don't want to come back to RTL level to create their IPs...

Behavioral IP Reuse, further improves design productivity

Side benefit of these C-level design automation, the IP reuse of signal processing IP is now becoming reality. The flow automation allows to have C-IPs quite independent of implementation constraints (technology, throughput, parameters), described at functional level, easy to modify to cope with new specification and easy to resynthesize. Another benefit: the size of the manual description (C instead of RTL) is reduced by roughly a factor 10. This reduces the time to modification (ECO) as well as the number of functional bugs manually introduced in the final silicon.

The link with Transactional Level Modelling (TLM) platform has to be enhanced. Prior to HLS flow, both TLM and RTL descriptions where done manually (Fig. 1.5).

HLS tools would be able to produce the TLM view needed for platform validation. However, the slowing-down of TLM standardization did not allow in 2006 neither H1-2007 to have a common agreement of what should be TLM 2.0 interface. This lack of standardization has penalized the convergence of TLM platform flow and C-level HW design flow. Designer community would benefit of such a common agreement between major players of the SystemC TLM community. More and more, we need CAD community to think in terms of flows in their global environment, and not in terms of tools alone.

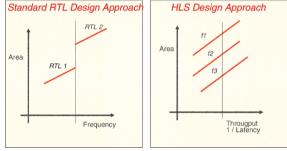

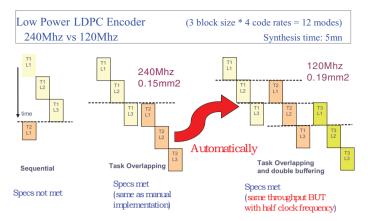

Another benefit of HLS tools automation is the micro-architecture exploration. Figure 1.6 basically describes a change of paradigm: clock frequency can be partially de-correlated from throughput constraints.

This means that, focusing on the functional constraints (throughput/latency), designer can explore several solutions fulfilling the specifications, but using various clock frequencies. Thanks to released clock constraint, the low-speed design will not have the area penalty of the high-speed solution. Combining this exploration

1 User Needs 5

Fig. 1.5 Convergence of TLM and design flows

#### Automatic scheduling : frequency becomes a parameter

Fig. 1.6 One benefit of automation: exploration

to memory partitioning and management exploration leads to some very interesting solutions. As an example, Fig. 1.7 shows that combining double buffering of an LDPC encoder to a division by 2 of the clock speed, produces a  $\times 0.63$  lower power solution for a 27% area penalty. The time-to-solution is dramatically reduced thanks to automation. The designer can then take the most appropriated solution depending on application constraints (area/power). Currently, power is estimated at RTL level, on automatically produced RTL, thanks to some specialized tools. Experience shows that power savings can be greatly improved at architectural level, compared to back-end design level.

There is currently no real power-driven synthesis solution known to us. This is one of the major needs we have for the future. Power driven synthesis will have to be much more than purely based on signals activity monitoring in the SoC buses. It will need also to take into account leakage current, memory consumption and will have to be compliant with multi-power-modes solutions (voltage and frequency scaling). There are many parameters to take into account to determine a power optimized solution, the ideal tool would have to take care of all these parameters in order to

P. Urard et al.

Fig. 1.7 HLS architecture explorations

Fig. 1.8 Medium term need: arithmetic optimizations

allow the designer to keep a high level of abstraction and to focus on functionality. For sure this would have to be based on some pre-characterization of the HW.

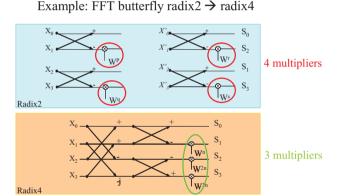

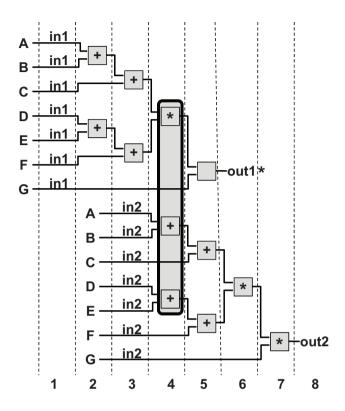

Now HLS is being deployed, new needs are coming out for more automation and more optimization. Deep arithmetic reordering is one of those needs. The current generation of tools is effectively limited in terms of arithmetic reordering. As an example: how to go from a radix2 FFT to a radix4 FFT without re-writing the algorithm? Figure 1.8 shows one direction new tools need to explore. Taylor Expansion Diagrams seems promising in this domain, but up to now, no industrial EDA tool has shown up.

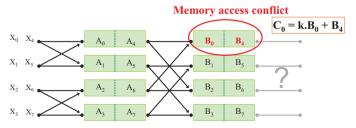

Finally after a few years spent in the C-level domain, it appears that some of the most limiting factors to exploration as well as optimization are memory accesses. If designer chose to represent memory elements by RAMs (instead of Dflip-flop), then the memory access order needs to be explicit in the input C code, as soon as this is not a trivial order. Moreover, in case of partial unroll of some FOR loops dealing

1 User Needs 7

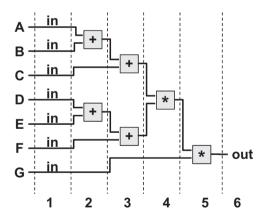

with data stored in a memory, the access order has to be re-calculated and C-code has to be rewritten to get a functional design. This can be resumed to a problem of memory precedence optimization. The current generation of HLS tools have a very low level of exploration of memory precedence, when they have some: some tool simply ignore it, creating non-functional designs! In order to illustrate this problem, let take an in-place FFT radix2 example. We can simplify this FFT to a bunch of butterflies, a memory (RAM) having the same width than the whole butterflies, and an interconnect. In a first trial, with a standard C-code, let flatten all butterflies (full unroll): we have a working solution shown in Fig. 1.9.

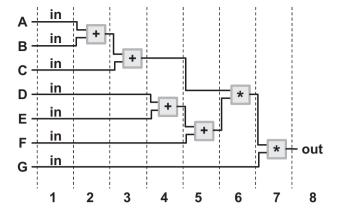

Keep in mind that during third stage, we store the memory the  $C_0 = K.B_0 + B_4$  calculation. Let now try to not completely unroll butterflies but allocate half of them (partial unroll). Memory will have the same number of memory elements, but twice deeper, and twice narrower. Calculation stages are shown in Fig. 1.10.

We can see that the third stage has a problem:  $C_0$  cannot be calculated in a single clock cycle as  $B_0$  and  $B_4$  are stored at two different addresses of the memory. With current tools generation, when  $B_0$  is not buffered, then RTL is not-functional

Example: 8 points FFT radix2

#### $\mathbf{C}_0 = \mathbf{k} \cdot \mathbf{B}_0 + \mathbf{B}_4$ $C_1$ C<sub>2</sub> В $A_2$ B<sub>3</sub> $C_3$ $\mathbf{B}_{4}$ $C_4$ $B_5$ $C_5$ A, $B_6$ $C_6$ $A_7$ $C_7$

Fig. 1.9 Medium term need: memory access problem

# Example: 8 points FFT radix2 Implementation test case: in-place & 4 data in parallel

Fig. 1.10 Medium term need: memory access problem

P. Urard et al.

Fig. 1.11 HLS flow: future enhancements at design space exploration level

because tools have weak check of memory precedence. HLS designers would need a tool that re-calculate memory accesses given the unroll factors and interface accesses. This would ease a lot the Design Space Exploration (DSE) work, leading to find much optimized solutions. This could also be part of higher level optimizations tools: DSE tools (Fig. 1.11).

Capacity of HLS tools is another parameter to be enhanced, even if tools have done enormous progresses those last years. The well known Moore's law exists and even tools have to follow the semi-conductor industry integration capacity.

As a conclusion, let underline that HLS tools are working, are used in production flows on advanced production chips. However, some needs still exist: enhancement of capacity, enhancement of arithmetic optimizations, or automation of memory allocation taking into account micro-architecture. We saw in the past many standalone solutions for system-level flows, industry now needs academias and CAD vendors to think in terms of C-level flows, not anymore stand-alone tools.

#### 1.2 Samsung's Viewpoints for High-Level Synthesis

## Joonhwan Yi and Hyukmin Kwon, Telecommunication R&D, Samsung Electronics Co.

High-level synthesis technology and its automation tools have been in the market for many years. However the technology is not mature enough for industry to widely accept it as an implementation solution. Here, our viewpoints regarding high-level synthesis are presented.

The languages that a high-level synthesis tool takes as an input often characterize the capabilities of the tool. Most high-level synthesis languages are C-variant including SystemC [1]. Some tools take C/C++ codes as inputs and some take SystemC as inputs. These languages differ from each other in several aspects, see

1 User Needs 9

|                          | ANSI C/C++          | SystemC                    |

|--------------------------|---------------------|----------------------------|

| Synthesizable code       | Untimed C/C++       | Untimed/timed SystemC      |

| Abstraction level        | Very high           | High                       |

| Concurrency              | Proprietary support | Standard support           |

| Bit accuracy             | Proprietary support | Standard support           |

| Specific timing model    | Very hard           | Standard support           |

| Complex interface design | Impossible          | Standard support, but hard |

| Ease of use              | Easy                | Medium                     |

**Table 1.1** The differences between C/C++ and SystemC as a high-level synthesis language

Table 1.1. Based on our experience, C/C++ is good at describing hardware behavior in a higher level than SystemC. On the other hand, SystemC is good at describing hardware behavior in a bit-accurate and/or timing-specific fashion than C/C++. High-level synthesis tools for C/C++ usually provide proprietary data types or directives because C/C++ has no standard syntax for describing timing. Of course, the degree of detail in describing timing by the proprietary mean is somewhat limited comparing to SystemC. So, there exists a trade-off between two languages. A hardware block can be decomposed into block body and its interface. Block body describes the behavior of the block and its interface defines the way of communication with the outer world of the block. A higher level description is preferred for a block body while a bit-accurate and timing-specific detail description needs to be possible for a block interface. Thus, a high-level synthesis tool needs to provide ways to describe both block bodies and block interfaces properly.

Generally speaking, high-level synthesis tools need to support common syntaxes and commands of C/C++/SystemC that are usually used to describe the hardware behavior at the algorithm level. They include arrays, loops, dynamic memories, pointers, C++ classes, C++ templates, and so on. Current high-level synthesis tools can synthesize some of them but not all. Some of these commands or syntaxes may not be directly synthesizable.

Although high-level synthesis intends to automatically convert an algorithm level specification of a hardware behavior to a register-transfer level (RTL) description that implements the behavior, it requires many code changes and additional inputs from designers [2]. One of the most difficult problems for our high-level synthesis engineers is that the code changes and additional information needed for desired RTL designs are not clearly defined yet. Behaviorally identical two high-level codes usually result in very different RTL designs with current high-level synthesis tools. Recall that RTL designs also impose many coding rules for logic synthesis and lint tools exist for checking those rules. Likewise, a set of well defined C/C++/SystemC coding rules for high-level synthesis should exist. So far, this problem is handled by a brute-force way and well-skilled engineers are needed for better quality of results.

One of the most notable limitations of the current high-level synthesis tools is not to support multiple clock domain designs. It is very common in modern hardware designs to have multiple clock domains. Currently, blocks with different clock domains should be synthesized separately and then integrated manually. Our

P. Urard et al.

high-level synthesis engineers experienced significant difficulties in integrating synthesized RTL blocks too. A block interface of an algorithm level description is usually not detailed enough to synthesize it without additional information. Also, integration of the synthesized block interface and the synthesized block body is done manually. Interface synthesis [4] is an interesting and important area for high-level synthesis.

Co-optimization of datapath and control logic is also a challenging problem. Some tools optimize datapath and others do control logic well. But, to our knowledge, no tool can optimize both datapath and control logic at the same time. Because a high-level description of hardware often omits control signals such as valid, ready, reset, test, and so on, it is not easy to automatically synthesize them. Some additional information may need to be provided. In addition, if possible, we want to define the timing relations between datapath signals and control signals.

High-level synthesis should take into account target process technology for RTL synthesis. The target library can be an application specific integrated circuit (ASIC) or a field programmable logic array (FPGA) library. Depending on the target technology and target clock frequency, RTL design should be changed properly. The understanding of the target technology is helpful to accurately estimate the area and timing behavior of resultant RTL designs too. A quick and accurate estimation of the results is also useful because users can quickly measure the effects of high-level codes and other additional inputs including micro architectural and timing information.

The verification of a generated RTL design against its input is another essential capability of high-level synthesis technology. This can be accomplished either by a sequential equivalence checking [3] or by a simulation-based method. If the sequential equivalence checking method can be used, the long verification time of RTL designs can be alleviated too. This is because once an algorithm level design  $D_h$  and its generated RTL design  $D_{RTL}$  are formally verified, fast algorithm level design verification will be sufficient to verify  $D_{RTL}$ . Sequential equivalence checking requires a complete timing specification or timing relation between  $D_h$  and  $D_{RTL}$ . Unless  $D_{RTL}$  is automatically generated from  $D_h$ , it is impractical to manually elaborate the complete timing relation for large designs.

Seamless integration to downstream design flow tools is also very important because the synthesized RTL designs are usually hard to understand by human. First of all, design for testability (DFT) of the generated RTL designs should be taken into account in high-level synthesis. Otherwise, the generated RTL designs cannot be tested and thus cannot be implemented. Secondly, automatic design constraint generation is necessary for gate-level synthesis and timing analysis. A high-level synthesis tool should learn all the timing behavior of the generated RTL designs such as information of false paths and multi-cycle paths. On the other hand, designers have no information about them.

We think high-level synthesis is one of the most important enabling technologies that fill the gap between the integration capacity of modern semiconductor processes and the design productivity of human. Although high-level synthesis is suffering from several problems mentioned above, we believe these problems will

1 User Needs 11

be overcome soon and high-level synthesis will prevail in commercial design flows in a near future.

#### 1.3 High Level Design Use and Needs in a Research Context

#### Alexandre Gouraud, France Telecom R&D

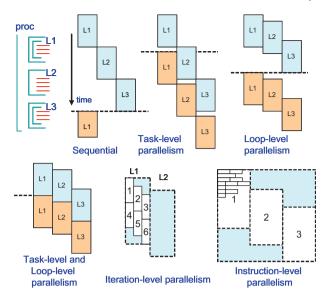

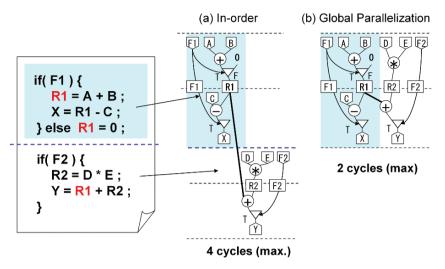

Implementing algorithms onto electronic circuits is a tedious task that involves scheduling of the operations. Whereas algorithms can theoretically be described by sequential operations, their implementations need better than sequential scheduling to take advantage of parallelism and improve latency. It brings signaling into the design to coordinate operations and manage concurrency problems. These problems have not been solved in processors that do not use parallelism at algorithm level but only at instruction level. In these cases, parallelism is not fully exploited. The frequency race driven by processor vendors shadowed the problem replacing operators' parallelism by faster sequential operators. However, parallelism remains possible and it will obviously bring tremendous gains in algorithms latencies. HLS design is a kind of answer to this hole, and opens a wide door to designers.

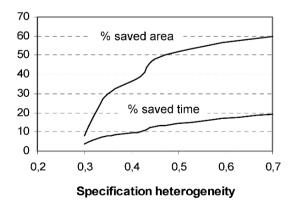

In research laboratories, innovative algorithms are generally more complex than in market algorithms. Rough approximations of their complexity are often the first way to rule out candidates to implementation even though intrinsic (and somehow often hidden) complexity might be acceptable. The duration of the implementation constrains the space of solutions to a small set of propositions, and is thus a bottleneck to exploration. HLS design tools bring to researchers a means to test much more algorithms by speeding up drastically the implementation phase. The feasibility of algorithms is then easily proved, and algorithms are faster characterized in term of area, latency, memory and speed.

Whereas implementation on circuits was originally the reserved domain of specialists, HLS design tools break barriers and bring the discipline handy to non-hardware engineers. In signal processing, for instance, it allows faster implementation of algorithms on FPGA to study their behavior in more realistic environment. It also increases the exploration's space by speeding up simulations.

Talking more specifically about the tools themselves, the whole stake is to deduce the best operations' scheduling from the algorithm description, and eventually from the user's constraints. A trade-off has to be found between user's intervention and automatic deduction of the scheduling in such a way that best solutions are not excluded by the tool and complicated user intervention is not needed.

In particular, state machine and scheduling signals are typical elements that the user should not have to worry about. The tool shall provide a way to show operations' scheduling, and eventually a direct or indirect way to influence it. The user shall neither have to worry about the way scheduling is implemented nor how effective this implementation is. This shall be the tool's job.

P. Urard et al.

Another interesting functionality is the bit-true compatibility with the original model/description. This guarantee spares a significant part of the costly time spent to test the synthesized design, especially when designs are big and split into smaller pieces. Whereas each small piece of code needed its own test bench, using HLS tools allows work on one bigger block. Only one test bench of the global entity is implemented which simplifies the work.

Models are generally complex, and their writing is always a meticulous task. If one can avoid their duplication with a different language, it is time saving. This raises the question whether architectural and timing constraints should be included inside the original model or not. There is no clear answer yet, and tools propose various interfaces described in this book. From a user's perspective, it is important to keep the original un-timed model stable. The less it is modified, the better it is manageable in the development flow. Aside from this, evolutions of the architecture along the exploration process shall be logged using any file versioning system to allow easy backward substitution and comparisons.

To conclude this introduction, it is important to point out that introduction of HLS tools should move issues to other fields like dimensioning of variables where tools are not yet available but the engineer's brains.

#### References

- 1. T. Grotker et al., System design with SystemC, Kluwer, Norwell, MA, 2002

- 2. B. Bailey et al., ESL design and verification, Morgan Kaufmann, San Mateo, 2007

- 3. Calypto design systems, available at http://www.calypto.com/products/index.html

- A. Rajawat, M. Balakrishnan, A. Kumar, Interface synthesis: issues and approaches, *Int. Conf. on VLSI Design*, pp. 92–97, 2000

#### **Chapter 2**

#### **High-Level Synthesis: A Retrospective**

Rajesh Gupta and Forrest Brewer

Abstract High-level Synthesis or HLS represented an ambitious attempt by the community to provide capabilities for "algorithms to gates" for a period of almost three decades. The technical challenge in realizing this goal drew researchers from various areas ranging from parallel programming, digital signal processing, and logic synthesis to expert systems. This article takes a journey through the years of research in this domain with a narrative view of the lessons learnt and their implication for future research. As with any retrospective, it is written from a purely personal perspective of our research efforts in the domain, though we have made a reasonable attempt to document important technical developments in the history of high-level synthesis.

**Keywords:** High-level synthesis, Scheduling, Resource allocation and binding, Hardware modeling, Behavioral synthesis, Architectural synthesis

#### 2.1 Introduction

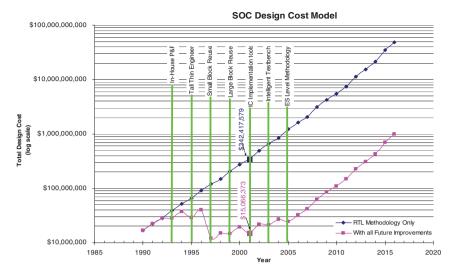

Modern integrated circuits have come to be characterized by the scaling of Moore's law which essentially dictates a continued doubling in the capacity of cost-efficient ICs every so many months (every 18 months in recent trends). Indeed, *capacity* and *cost* are two major drivers of the microelectronics based systems on a chip (or SOC). A pad limited die of 200 pins on a 130 nm process node is about 50 square millimeters in area and comes to about \$5 or less in manufacturing and packaging costs per part given typical yield on large volumes of 100,000 units or more. That is area sufficient to implement a large number of typical SOC designs without pushing the envelope on die size or testing or packaging costs. However, the *cost of design* continues to rise. Figure 2.1 shows an estimate of design costs which were estimated to be around US\$15M, contained largely through continuing

Fig. 2.1 Rising cost of IC design and effect of CAD tools in containing these costs (courtesy: Andrew Kahng, UCSD and SRC)

advances in IC implementation tools. Even more importantly, silicon architectures – that is, the architecture and organization of logic and processing resources on chip – are of critical importance. This is because of a tremendous variation in the realized efficiency of silicon as a computational fabric. A large number of studies have shown that energy or area efficiency for a given function realized on a silicon substrate can vary by two to three orders of magnitude. For example, the power efficiency of a microprocessor-based design is typically 100 million operations per watt, where as reprogrammable arrays (such as Field Programmable Gate Arrays or FPGAs) can be 10-20×, and a custom ASIC can give another 10× gain. In a recent study, Kuon and Rose show that ASICs are 35× more area efficient that FPGAs [1]. IC design is probably one of the few engineering endeavors that entail such a tremendous variation in the quality of solutions in relation to the design effort. If done right, there is a space of 10-100× gain in silicon efficiency when realizing complex SOCs. However, realizing the intrinsic efficiency of silicon in practice is an expensive proposition and tremendous design effort is expended to reach state power, performance and area goals for typical SOC designs. Such efforts invariably lead to functional, performance, and reliability issues when pushing limits of design optimizations. Consequently, in parallel with the Moore's law, each generation of computer-aided design (CAD) researchers has sought to disrupt conventional design methodologies with the advent of high-level design modeling and tools to automate the design process. This pursuit to raise the abstraction level at which designs are modeled, captured, and even implemented has been the goal of several generations of CAD researchers. Unfortunately, thus far, every generation has come away with mixed success leading to the rise of yet another generation that seems to have got it right. Today, such efforts are often lumped under the umbrella term of ESL or Electronic System Level design which in turn means a range of activities from algorithmic design and implementation to virtual system prototyping to function-architecture co-design [43].

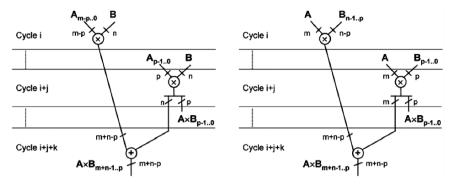

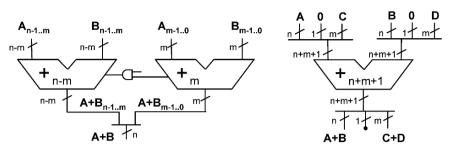

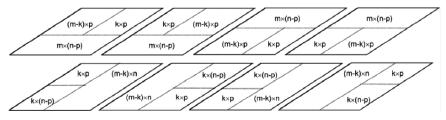

#### 2.2 The Vision Behind High-Level Synthesis

Mario Barbacci noted in late 1974 that in theory one could "compile" the instruction set processor specification (then in the ISPS language) into hardware, thus setting up the notion of design synthesis from a high-level language specification. High-level Synthesis in later years will thus come to be known as the process of automatic generation of hardware circuit from "behavioral descriptions" (and as a distinction from "structural descriptions" such as synthesizable Verilog). The target hardware circuit consists of a structural composition of data path, control and memory elements. Accordingly, the process was also variously referred to as a transformation "from behavior to structure." By the early eighties, the fundamental tasks in HLS had been decomposed into hardware modeling, scheduling, resource allocation and binding, and control generation. Briefly, modeling concerned with capturing specifications as program-like descriptions and making these available for downstream synthesis tasks via a partially-ordered description that is designed to expose concurrency available in the description. Task scheduling schedules operations by assigning these to specific clock cycles or by building a function (i.e., a scheduler) that determines execution time of each operation at the runtime. Resource allocation and binding determine the resources and their quantity needed to build the final hardware circuit. Binding refers to specific binding of an operation to a resource (such as a functional unit, a memory, or an access to a shared resource). Sometimes module selection has been used to describe the problem of selecting an appropriate resource type from a library of modules under a given metric such as area or performance. Finally, control generation and optimization sought to synthesize a controller to generate appropriate control signals according to a given schedule and binding of resources. This decomposition of HLS tasks was for problem solving purposes; almost all of these subtasks are interdependent.

Early HLS had two dominant schools of thought regarding scheduling: fixed latency constrained designs (such as early works by Pierre Paulin, Hugo DeMan and their colleagues) and fixed resource constrained designs (such as works by Barry Pangrle, Howard Trickey and Kazutoshi Wakabayashi). In the former case, resources are assigned in a minimal way to meet a clock latency goal, in the latter, minimal time schedules are derived given a set of pre-defined physical resources. The advantage of fixed latency is easy incorporation of the resulting designs into larger timing-constrained constructions. These techniques have met with success in the design of filters and other DSP functions in practical design flows. Fixed resource models allowed a much greater degree of designer intervention in the selection and constraint of underlying components, potentially allowing use of the tools in area or power-constrained situations. They also required more

complex scheduling algorithms to accommodate the implied constraints inherent in the chosen hardware models. Improvements in the underlying algorithms later allowed for simultaneous consideration of timing and resource constraints; however, the complexity of such optimization limits their use to relatively small designs or forces the use of rather coarse heuristics as was done in the Behavioral Compiler tool from Synopsys. More recent scheduling algorithms (Wave Scheduling, Symbolic Scheduling, ILP and Interval Scheduling) allow for automated exploration of speculative execution in systematic ways to increase the available parallelism in a design. At the high end of this spectrum, the distinction between static (pre-determined execution patterns) and dynamic (run-time determined execution patterns) are blurred by the inclusion of arbitration and local control mechanisms.

#### 2.3 History

High-level synthesis (HLS) has been a major preoccupation of CAD researchers since the late 1970s. Table 2.1 lists major time points in the history of HLS research through the eighties and the nineties; this list of readings would be typical of a researcher active in the area throughout this period. As with any history, this is by no means a comprehensive listing. We have intentionally skipped some important developments in this decade since these are still evolving and it is too early to look back and declare success or failure.

Early work in HLS examined scheduling heuristics for data-flow designs. The most straightforward approaches include scheduling all operations as soon as possible (ASAP) and scheduling the operations as late as possible (ALAP) [5–8]. These were followed by a number of heuristics that used metrics such as urgency [9] and mobility [10] to schedule operations. The majority of the heuristics were derived from basic list scheduling where operations are scheduled relative to an ordering based on control and data dependencies [11-13]. Other approaches include iteratively rescheduling the designs [14] and scheduling along the critical path through the behavioral description [15]. Research in resource allocation and binding techniques have sought varying goals including reducing registers, reducing functional units, and reducing wire delays and interconnect costs [3–5]. Clique partitioning and clique covering were favorite ingredients to solving module allocation problems [6] and to find the solution of a register-compatibility graph with the lowest combined register and interconnect costs [16]. Network flow formulations were used to bind operations and registers at each time step [18] and to perform module allocation while minimizing interconnect [17].

Given the dependent nature of each task within HLS, researchers have focused on performing these tasks in parallel, namely through approaches using integer linear programming (ILP) [19–22]. In the OSCAR system [21], a 0/1 integer-programming model is proposed for simultaneous scheduling, allocation, and binding. Wilson and co-authors [22] presented a generalized ILP approach to provide an integrated solution to the various HLS tasks. In terms of design performance, pipelining

Table 2.1 Major timepoints in the historical evolution of HLS through the 1980s and 1990s

| Year    | Authors                                                                                                                                                                                                                                                            |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1972–75 | Barbacci, Knowles: ISPS description                                                                                                                                                                                                                                |

| 1978    | McFarland: ValueTrace (VT) model for behavioral representation                                                                                                                                                                                                     |

| 1980    | Snow's Thesis that was among the first to show use of CDFG as a synthesis specification                                                                                                                                                                            |

| 1981    | Kuck and co-authors advance compiler optimizations (POPL)                                                                                                                                                                                                          |

| 1983    | Hitchcock and Thomas on datapath synthesis                                                                                                                                                                                                                         |

| 1984    | Tseng and Siewiorek work on bus-style design generator                                                                                                                                                                                                             |

| 1984    | Emil Gircyz thesis on using ADA for modeling hardware, precursor to VHDL                                                                                                                                                                                           |

| 1985    | Kowalski and Thomas on use of AI techniques for design generation                                                                                                                                                                                                  |

| 1985    | Pangrle on first look-ahead/clock independent scheduler                                                                                                                                                                                                            |

| 1985    | Orailoglu and Gajski: DESCART silicon compiler; Nestor and Thomas on synthesis from interfaces                                                                                                                                                                     |

| 1986    | Knapp on AI planning; Brewer on Expert System; Marwedel on MIMOLA; Parker on MAHA pipelined synthesis; Tseng, Siewiorek on behavioral synthesis                                                                                                                    |

| 1987    | Flamel by Tricky; Paulin on force-directed scheduling; Ebcioglu on software pipelining                                                                                                                                                                             |

| 1988    | Nicolau on tree-based scheduling; Brayton and co-authors: Yorktown silicon compiler; Thomas: System architect's workbench (SAW); Ku and DeMicheli on HardwareC; Lam: on software pipelining; Lee on synchronous data flow graphs for DSP modeling and optimization |

| 1989    | Wakabayashi on condition vector analysis for scheduling; Goosens and DeMan on loop scheduling                                                                                                                                                                      |

| 1990    | Stanford Olympus synthesis system; McFarland, Parker and Camposano overview; DeMan on Cathedral II                                                                                                                                                                 |

| 1991    | Hilfinger's Silage and its use by DeMan and Rabaey on Lager DSP Synthesis;<br>Camposano: Path based scheduling; Stock, Bergamaschi; Camposano and Wolf book<br>on HLS; Hwang, Lee and Hsu on Scheduling                                                            |

| 1992    | Gajski HLS book; Wolf on PUBSS                                                                                                                                                                                                                                     |

| 1993    | Radevojevic, Brewer on Formal Techniques for Synthesis                                                                                                                                                                                                             |

| 1994    | DeMicheli book on Synthesis and Optimization covering a good fraction of HLS                                                                                                                                                                                       |

| 1995    | Synopsys announces Behavioral Compiler                                                                                                                                                                                                                             |

| 1996    | Knapp book on HLS                                                                                                                                                                                                                                                  |

|         | Another decade of various compiler + synthesis approaches                                                                                                                                                                                                          |

| 2005    | Synopsys shuts down Behavioral Compiler                                                                                                                                                                                                                            |

was explored extensively for data-flow designs [10, 13, 23–25]. Several systems including HAL [10] and Maha [15] were guided by user-specified constraints such as pipeline boundaries or timing bounds in order to distribute resources uniformly and minimize the critical path delay. Optimization techniques such as algebraic transformations, retiming and code motions across multiplexers showed improved synthesis results [26–28].

Throughout this period, the quality of synthesis results continued to be a major preoccupation for the researchers. Realizing the direct impact of how control structures affected the quality of synthesized circuits, several researchers focused their efforts on augmenting HLS to handle complex control flow. Tree-based scheduling [29] removes all the join nodes from a design so that the control-data flow graph (CDFG) becomes a tree and speculative code motion can be applied. The PUBSS

approach [30] extracts scheduling information in a behavioral finite state machine (BFSM) model and generates a schedule using constraint-solving algorithms. NEC created the CVLS approach [31–33] that uses condition vectors to improve resource sharing among mutually exclusive operations. Radivojevic and Brewer [34] provide an exact symbolic formulation that schedules each control path independently and then creates an ensemble schedule of valid control paths. The Waveschedule approach minimizes the expected number of cycles by using speculative execution. Several other approaches [35–38] support generalized code motions during scheduling in synthesis systems where operations can be moved globally irrespective of their position in the input. Prior work examined pre-synthesis transformations to alter the control flow and extract the maximal set of independent operations [39,40]. Li and Gupta [41] restructure control flow to extract common sets of operations with conditionals to improve synthesis results.

Compiler transformations can further improve HLS, although they were originally developed for improving code efficiency for sequential program execution. Prominent among these were variations on common sub-expression elimination (CSE) and copy propagation which are commonly seen in software compilers [1,2]. Although the basic transformations such as dead code elimination and copy propagation can be used in synthesis, other transformations need to be re-instrumented for synthesis by incorporating ideas of mutual exclusivity of operations, resource sharing, and hardware cost models. Later attempts in the early 2000s explored parallelizing transformations to create a new category of HLS synthesis that seeks to fundamentally overcome limitations on concurrency inherent in the input algorithmic descriptions by constructing methods to carry out large-scale code motions across conditionals and loops [42].

#### 2.4 Successes and Failures

While the description above is not intended to be a comprehensive review of all the technical work, it does beg an important question: once the fundamental problems in HLS were identified with cleanly laid out solutions, why didn't the progress in problem understanding naturally lead to tools as had been the case with the standard cell RTL design flows?

There is an old adage in computer science: "Artificial Intelligence can never be termed a 'success' – the techniques that worked such as efficient logic data-structures, data mining and inference based reasoning became valuable on there own – the parts that remain unsolved retain the title 'Artificial Intelligence." In many ways, the situation is similar in High Level Synthesis; simple-to-apply techniques were moved out of that context and into general use. For example, the Design Compiler® tool from Synopsys regularly uses allocation and binding optimizations on arithmetic and other replicated units in conventional 'logic optimization' runs. Some of the more clever control synthesis techniques have also been incorporated into that tool's finite state machine synthesis options.

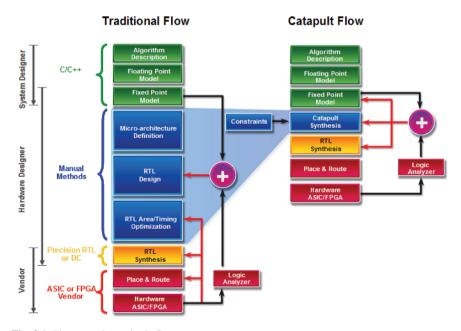

Many of the ideas which did not succeed in the general ASIC context have made a comeback in the somewhat more predictable application of FPGA synthesis with tools such as Mentor's Catapult-C supporting a subset of the C-programming language for direct synthesis into FPGA designs. A number of products mapping designs originally specified in MatLab's M language or in specialized component libraries for LabView have appeared to directly synthesize designs for digital signal processing in FPGA's. Currently, these tools range in complexity from hardware macro-assemblers which do not re-bind operation instances to the fairly complex scheduling supported by Catapult-C. The practicality of these tools is supported by the very large scale of RTL designs that can be mapped into modern large FPGA devices.

On the other hand, the general precepts of High Level Synthesis have not been so well adopted by the design community nor supported by existing synthesis systems. There have been several explanations in the literature: lack of a well-defined or universally accepted intermediate model for high-level capture, poor quality of synthesis results, lack of verification tools, etc. We believe the clearest answer is found in the classical proverb regarding dogs not liking the dogfood. That is, the circuit designers who were the target of such tools and methods did not really care about the major preoccupation of solving the scheduling and allocation problems. For one, this was a major part of the creativity for the RTL implementers who were unlikely to let go of the control of clock cycle boundaries, that is, the explicit specification of which operation happened on which cycle. So, in a way, the targeted users of HLS tools were being told do something differently that they already did very well. By contrast, tools took away the controllability, and due to the semantic gap between the designer intent and the high-level specification, synthesis results often fell short of the quality expectations. A closer examination leads us to point to the following contributing factors:

- a. The so-called high-level specifications in reality grew out of the need for simulation and were often little more than an input language to make a discrete event simulator reproduce a specific behavior.

- The complexity of timing constraint specification and analysis was grossly underestimated, especially when a synthesizer needs to utilize generalized models for timing analysis.

- c. Design metrics were fairly naïve: the so-called data-dominated versus control-dominated simplifications of the cost model grossly mis-estimated the true costs and, thus, fell short on their value in driving optimization algorithms. By contrast, in specific application areas such as digital signal processing where the input description and cost models were relatively easier to define, the progress was more tangible.

- d. The movement from a structural to a behavioral description the centerpiece of HLS – presented significant problems in how the design hierarchy was constructed. The parameterization and dynamic elaboration of the major hierarchy components (e.g., number of times a loop body is invoked) requires dramatically different synthesis methods that were just not possible in a description that

essentially looks identical to a synthesis tool. A fundamental understanding of the role of structure was needed before we even began to capture the design in a high-level language.

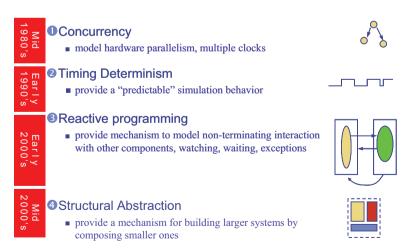

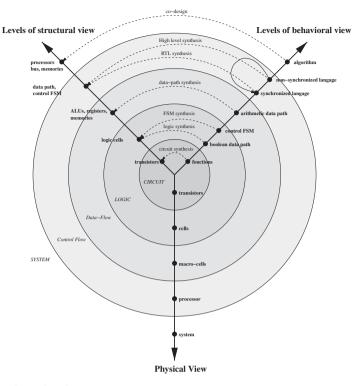

#### 2.5 Lessons Learnt

The notion of describing a design as a high-level language program and then essentially "compiling" into a set of circuits (instead of assembly code) has been a powerful attractor to multiple generations of researchers into HLS. There are, however, complexities in this form of specification that can ruin an approach to HLS. To understand this, consider the semantic needs when building a hardware description language (HDL) from a high-level programming language. There are four basic needs as shown in Fig. 2.2: (1) a way to specify concurrency in operations, (2) ensure timing determinism to enable a designer build a "predictable" simulation behavior (even as the complete behavior is actually unspecified), (3) ensure effective modeling of the reactive aspects of hardware (non-terminating behavior, event specifications), and (4) capture structural aspects of a design that enables an architect to build larger systems by instantiating and composing from smaller ones.

#### 2.5.1 Concurrency Experiments

Of the four requirements listed in Fig. 2.2, concurrency was perhaps the most dominant preoccupation of HLS researchers since the early years for a good reason: one of the first things that a HLS tool has to do when presented with an

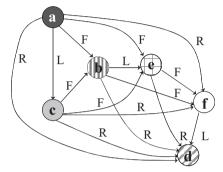

Fig. 2.2 Semantic needs from programming to hardware modeling and time-line over which these aspects were dominant in the research literature

algorithmic description in a programming language is to extract the parallelism inherent in the specification. The most common way was to extract data-flow graphs from the description based on a def-use dependency analysis of operations. Since these graphs tended to be disjoint making it hard for the synthesis algorithms to operate, they were often combined with nodes and edges to represent flow of control. Thus, the combined Control-Data Flow Graphs or CDFG were commonly used. Most of these models did not capture use of any structured memory blocks, which were often treated as separate functional or structural blocks. By and large, CDFGs were used to implement synthesis tasks as graph operations (for example, labeled graphs representing scheduling, and binding results). However, hierarchical modeling was a major issue. Looking back, there were three major lessons that we can point to. First, not all CDFGs were the same. Even if matched structurally, the semantic variations on graphs were tremendous: operational semantics of the nodes, what edges represent, etc. An interesting innovation in this area was the attempt to move all non-determinism (in operations, timing) to the graph model hierarchy in the Stanford Intermediate Format (SIF) graph. In a SIF graph, loops and conditions were represented as separate graph bodies, where a body corresponded to each conditional invocation of a branch. Thus, operationally the uncertainty due to control flow (or synchronization operations) was captured as the uncertainty in calling a graph. It also made SIF graphs DAGs, thus enabling efficient algorithms for HLS scheduling and resource allocation tasks in the Olympus Synthesis System.

The second lesson was also apparent from the Olympus system that employed a version of C, called HardwareC, which enabled specification of concurrent operations at arbitrary levels of granularity: two operations could be scheduled in parallel, sequentially, or in a data-parallel fashion by enclosing them using three different set of parentheses; and then the composition could also be similarly composed in one of three ways, and so on. While it enabled a succinct description of complex dependency relationships (as Series-Parallel graphs), it was counter-intuitive to most designers: a small change on a line could have a significant (and non-obvious) impact on an operation several pages away from the line changed, leading designers to frustrating simulation runs. Experience in this area has finally resulted in most HDLs settling for concurrency specification at an aggregate "process" level, whereas processes themselves are often (though not always, see structural specifications later) sequential.

The third, and perhaps, the most important lesson we learnt when modeling designs was regarding methods used to go from a high-level programming language (HLL) to an HDL. Broadly speaking, there are three ways to do it: (1) as a syntactic add-on to capture "hardware" concepts in the specification. Examples include "process", "channel" in HardwareC, "signals" in VHDL etc. (2) Overload semantics of existing constructs in a HLL. A classic example is that an assignment in VHDL implies placement of an event *in future*. (3) Use existing language level mechanisms to capture hardware-specific concepts using libraries, operator overloading, polymorphic types, etc., as is the case in SystemC. An examination of HDL history would demonstrate the use of these three methods in roughly the same order. While syntactical changes to existing HLL were common-place in the early years of

HDL modeling, later years have seen a greater reliance on library-based HDLs due to a combination of greater understanding of HDL needs combined with advances in HLLs towards sophisticated languages that provide creative ways to exploit type mechanisms, polymorphism and compositional components.

## 2.5.2 Timing Capture and Analysis for HLS

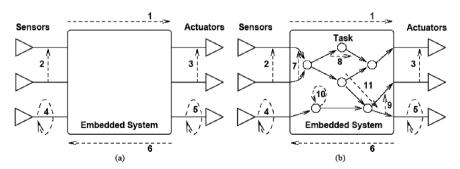

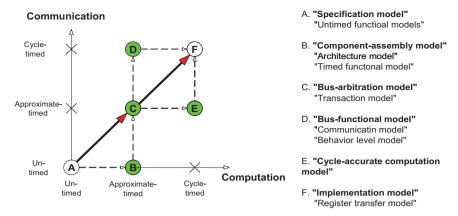

The early nineties saw an increased focus on the capture of timing behavior in HLS. This was also the time when the term "embedded systems" entered the vocabulary of researchers in this field, and it consequently caused researchers to look at high-level IC design as a *system* design problem. Thus, input descriptions were beginning to look like descriptions of components in temporal interaction with the environment as shown in Fig. 2.3 below. Thus, one could specify and analyze timing requirements separately from the functional behavior of the system design.

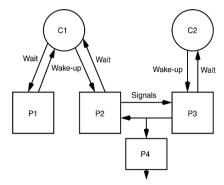

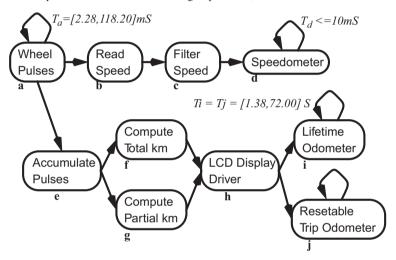

Accordingly, the behavioral models evolved: from the early years of functionality and timing models to their convergence into single "operation-event" graphs of Amon and Borriello, we made a full circle to once again separate timing and functional models. Building upon a long line of research on event graphs, Dasdan and Gupta proposed generalized task graph models consisting of tasks as nodes and communications between tasks as edges that can carry multiple tokens. The nodes could be composed according to a classification of tasks: an AND task represents actions that are performed after conjunction of its predecessor tasks have completed, whereas an OR task can initiate once any of its predecessors have completed execution. The tasks could also optionally skip tokens, thereby capturing realistic timing response to events. This structure allowed us to generate discrete event models directly from the task graphs that can be used for "timing simulation" even when the functional behavior of the overall system has not been devised beyond, of course, the general structure of the tasks (Fig. 2.4).

Works such as this enabled researchers to define and make progress on high-level design methodologies that were "timing-driven." While this was a tremendously useful exercise, its applicability was basically limited by the lack of timing detail

Fig. 2.3 A system design conceptualized as one in temporal interaction with the environment

Fig. 2.4 Conceptual model of Scenic consisting of processes, clocks and reactions

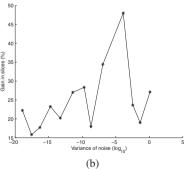

**Fig. 2.5** Example of a timing simulation for an automotive information display that uses normally distributed acceleration and deceleration periods (mean: 20 s, deviation: 1 s). The vehicle response is normally distributed as well. The simulation has been created directly from the semantics of the task graph model without detailed functional implementation